Titanium Interfaces User Guide

MIPI DPHY RX Interface Designer Settings

The following tables describe the settings for the Titanium MIPI DPHY RX blocks in the

Interface Designer.

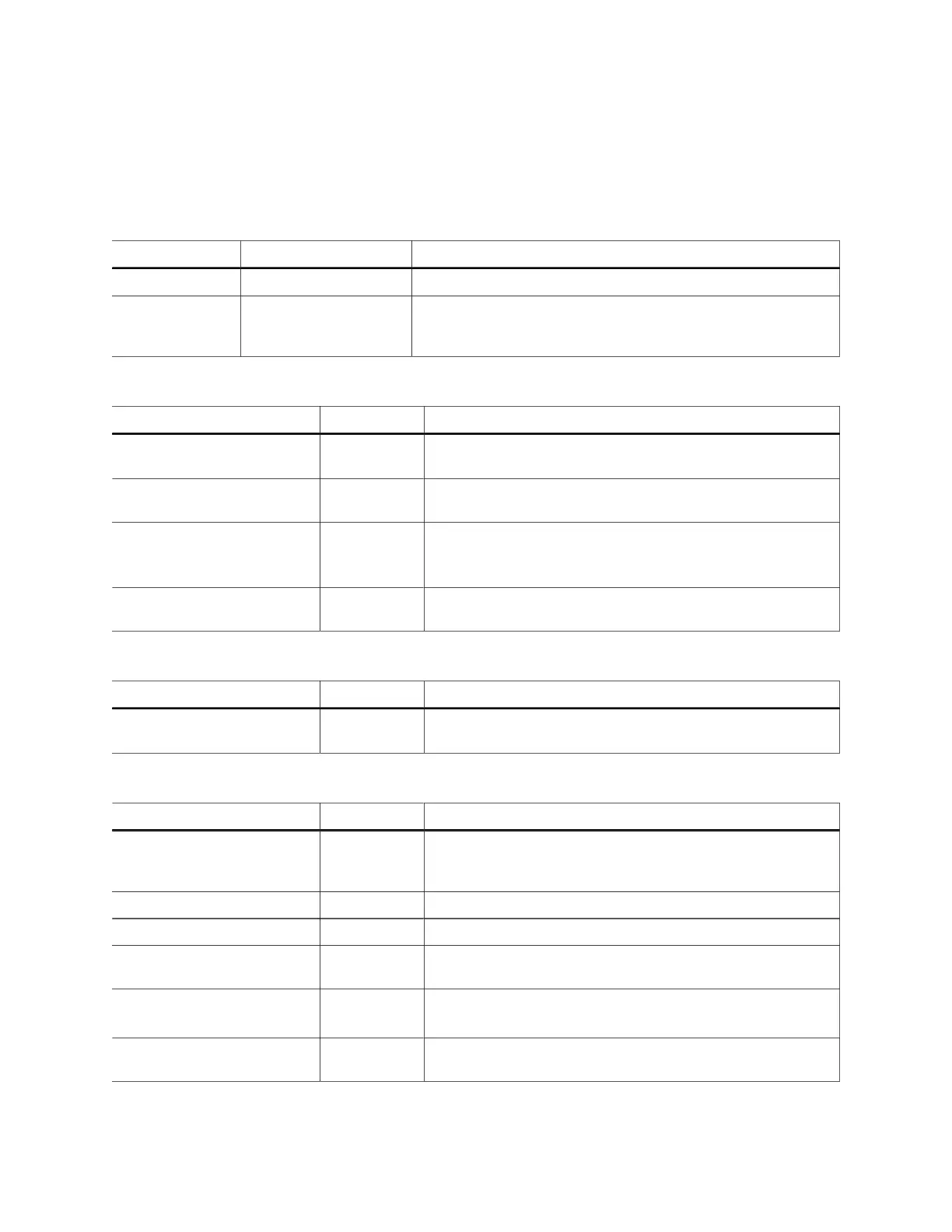

Table 74: Base Tab

Parameter Choices Notes

Instance Name User defined

MIPI RX Resource None, MIPI_RX0,

MIPI_RX1,

MIPI_RX2, MIPI_RX3

Choose the resource.

Table 75: Control/Status Tab

Option Choices Notes

Calibration Clock Frequency

(MHz)

80 - 120 Specify the frequency. Default: 0

<description> Pin Name User defined Control and status pin names. Efinix recommends that you use

the defaults.

HS Transmit Byte/Word Clock

Connection Type

gclk, rclk Choose whether to connect to a global clock (gclk) or regional

clock (rclk).

Default: gclk

Invert Excape Mode Transmit

Clock Pin

On or off Turn on to invert the clock.

Table 76: Clock Lane Tab

Option Choices Notes

<description> Pin Name User defined Clock lane pin names. Efinix recommends that you use the

defaults.

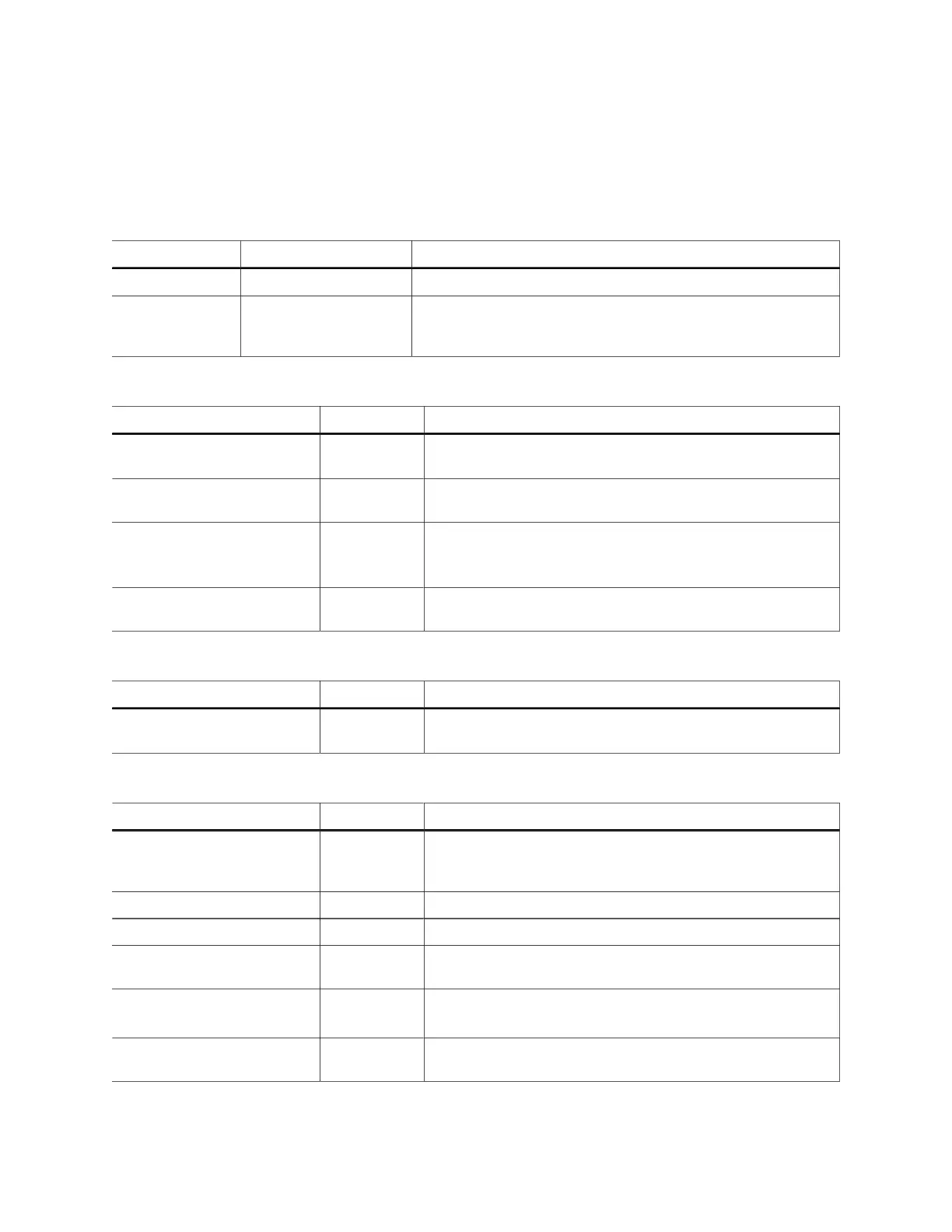

Table 77: Data Lane Tab

Option Choices Notes

Enable Turn-around Feature in

Data Lane 0

On or off Lane 0 can operate as a bi-directional data lane when this

option is on.

Default: on

Number of data lanes 1, 2, 4 Choose the number of lanes. Default: 4

Width of the data bus 8, 16 Specify the width. Default: 8

Lane n: Escape Mode Receive

Clock Pin Name

User defined Specify the clock.

Lane 0: Escape Mode Receive

Clock Connection Type

normal, rclk normal: Default. The clock signal is an input signal to the core.

rclk: The clock signal is feeding the regional clock network.

Lane n: <description> Pin

Name

User defined Data lane pin names. Efinix recommends that you use the

defaults.

www.efinixinc.com 119

Loading...

Loading...