Titanium Interfaces User Guide

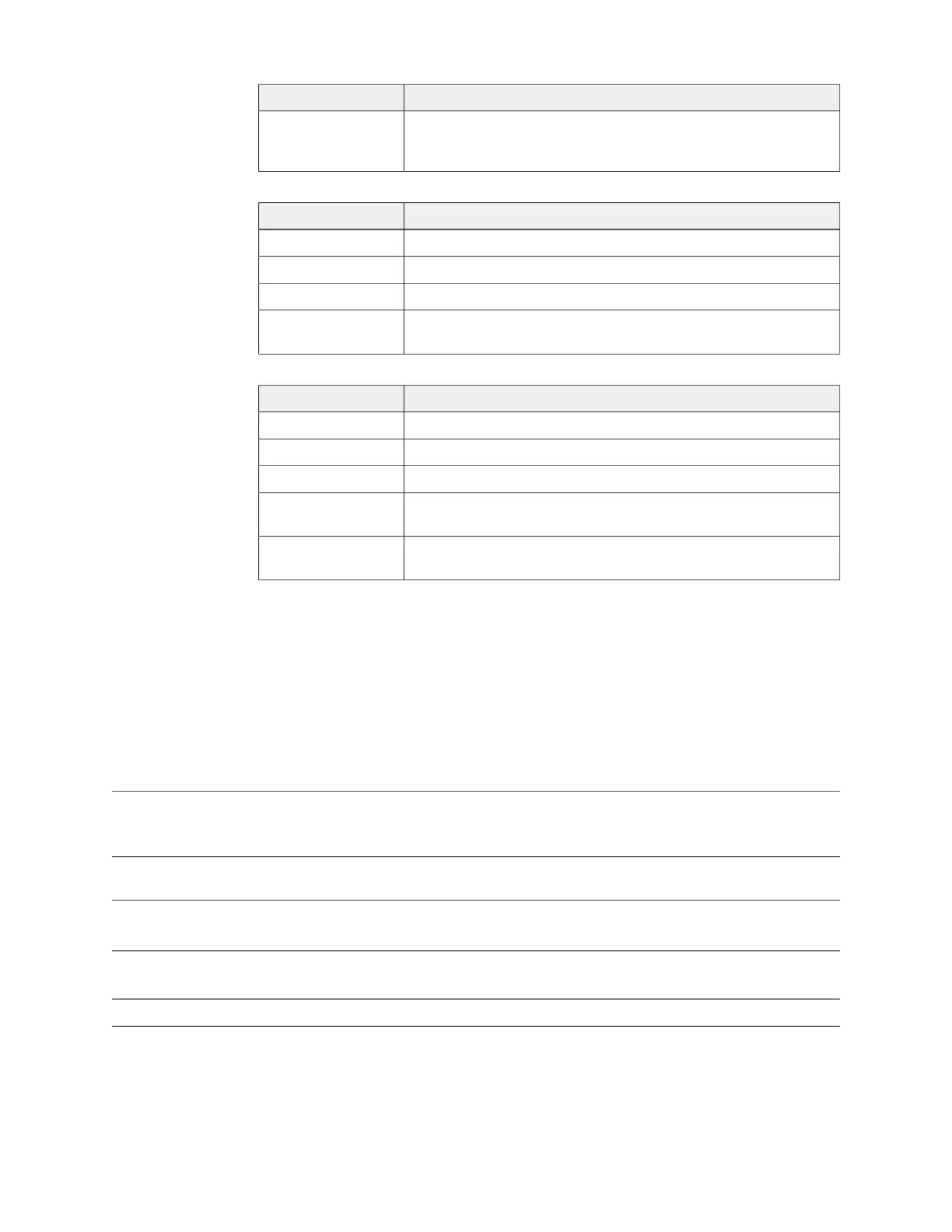

Option Description

The fast clock (INFASTCLK) should be 4 times faster than the slow

clock (INCLK). . The serial clock phase shift should be between 45

and 135 degrees.

2. Add a GPIO block with these settings to provide the reference clock input to the PLL:

Option Description

Mode Input

Pin Name Any

Connection Type pll_clkin

GPIO Resource Assign the dedicated PLL_CLKIN pin that corresponds to the PLL

you chose.

3. Add a GPIO block with these settings:

Option Description

Mode input

Register Option register

Enable Serialization Turn on

Clock Pin Name Use the slow clock output name that corresponds to the PLL you

chose.

Serial Clock

Pin Name

Use the fast clock output name that corresponds to the PLL you

chose.

4. Repeat step 3 for each RX deserializer you want to implement.

Design Check: GPIO Messages

When you check your design, the Interface Designer applies design rules to your

configuration settings. The following tables show some of the error and warning messages

you may encounter and explains how to fix them.

bus_rule_members_consistent (error)

Message Bus <name> has mismatch properties with its members

Members of bus <name> has inconsistent shared pin/register settings with <member>:

<inconsistent_members_name>

To fix The properties you have set for the bus are inconsistent with the settings for the bus

members. Review the settings and fix any mismatches.

bus_rule_name (error)

Message Bus name is empty

Valid characters are alphanumeric characters with dash and underscore only

To fix Specify a valid bus name.

www.efinixinc.com 56

Loading...

Loading...