Titanium Interfaces User Guide

MIPI DPHY TX Interface Designer Settings

The following tables describe the settings for the Titanium MIPI DPHY TX blocks in the

Interface Designer.

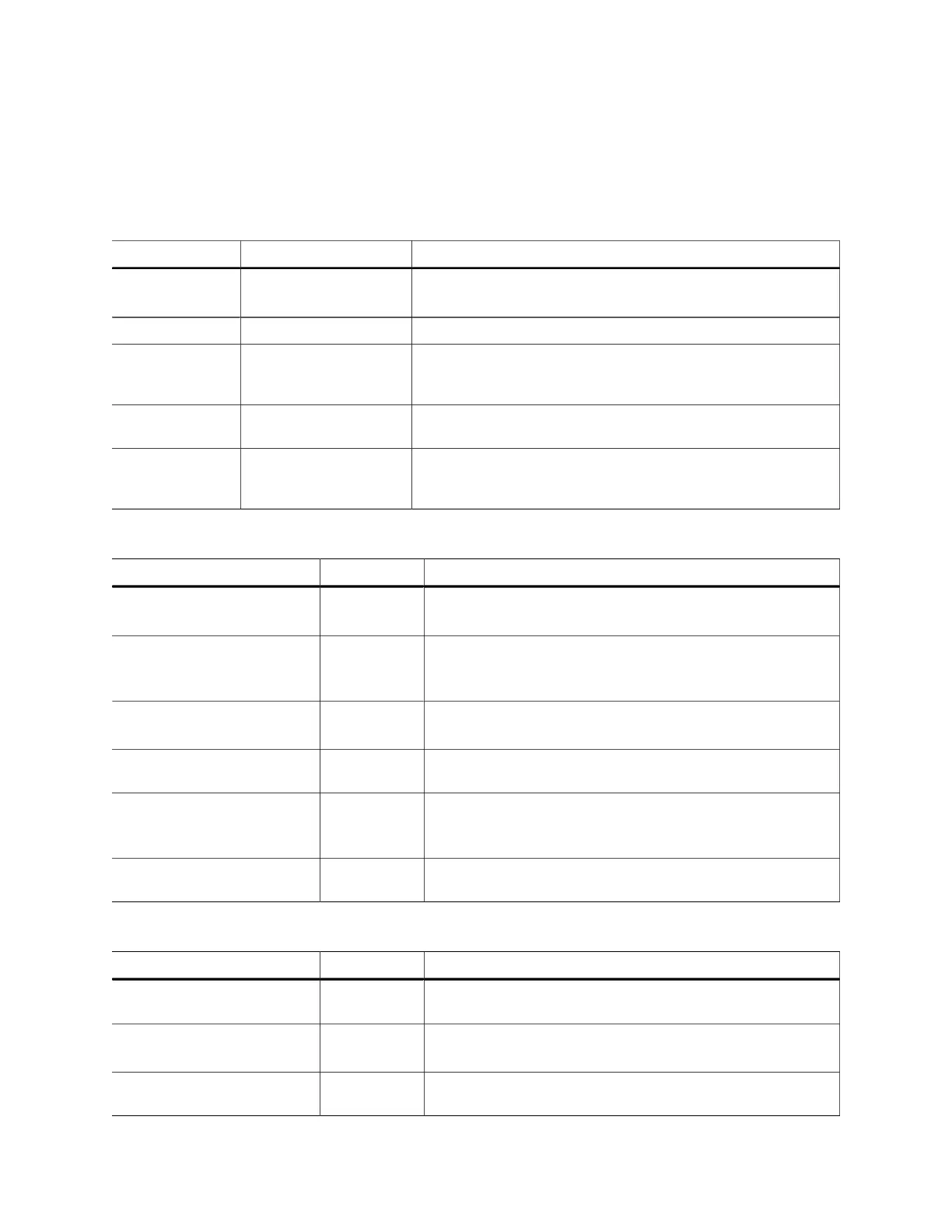

Table 68: Base Tab

Parameter Choices Notes

PHY bandwidth in

Mbps

Integer up to 2500 Specify the bandwidth.

Default: 2500

Instance Name User defined

MIPI TX Resource None, MIPI_TX0,

MIPI_TX1,

MIPI_TX2, MIPI_TX3

Choose the resource.

Reference Clock

Frequency

12.0, 19.2, 25.0,

26.0, 27.0, 38.4, 52.0

Choose the frequency for the reference clock.

Reference Clock

Source Type

core, gpio, pll Choose which resource generates the reference clock. For gpio

and pll, the Block Editor shows you which resource to connect as

the reference clock. For core, you specify the clock name.

Table 69: Control/Status Tab

Option Choices Notes

SSC Amplitude for MIPI

Internal PLL

0 - 200 Spread-spectrum clock frequency setting. 20 - 200 kHz.

Default: 2

SSC Initial Amplitude for MIPI

Internal PLL

0 - 50000 Spread-spectrum clock initial spread down amount. 2500 -

50000 ppm.

Default: 3

SSC Period for MIPI Internal

PLL

0 - 50000 Spread-spectrum clock amount. 2500 to 50000 ppm.

Default: 1

<description> Pin Name User defined Control and status pin names. Efinix recommends that you use

the defaults.

HS Transmit Byte/Word Clock

Connection Type

gclk, rclk Choose whether to connect to a global clock (gclk) or regional

clock (rclk).

Default: gclk

Invert Excape Mode Transmit

Clock Pin

On or off Turn on to invert the clock.

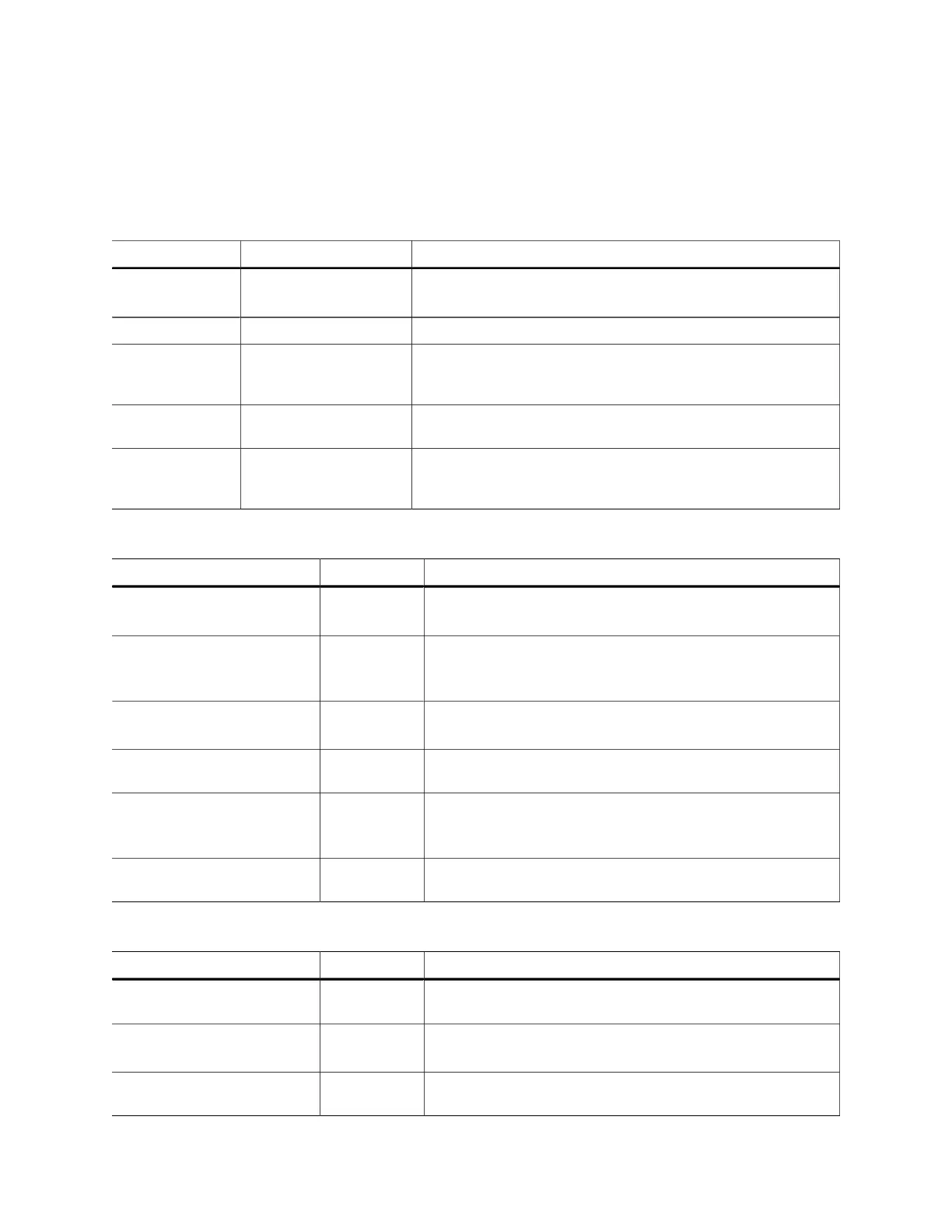

Table 70: Clock Lane Tab

Option Choices Notes

Escape Mode Receive Clock

Pin Name

User defined Specify the clock name.

Escape Mode Receive Clock

Connection Type

normal, rclk normal: Default. The clock signal is an input signal to the core.

rclk: The clock signal is feeding the regional clock network.

<description> Pin Name User defined Clock lane pin names. Efinix recommends that you use the

defaults.

www.efinixinc.com 117

Loading...

Loading...