Titanium Interfaces User Guide

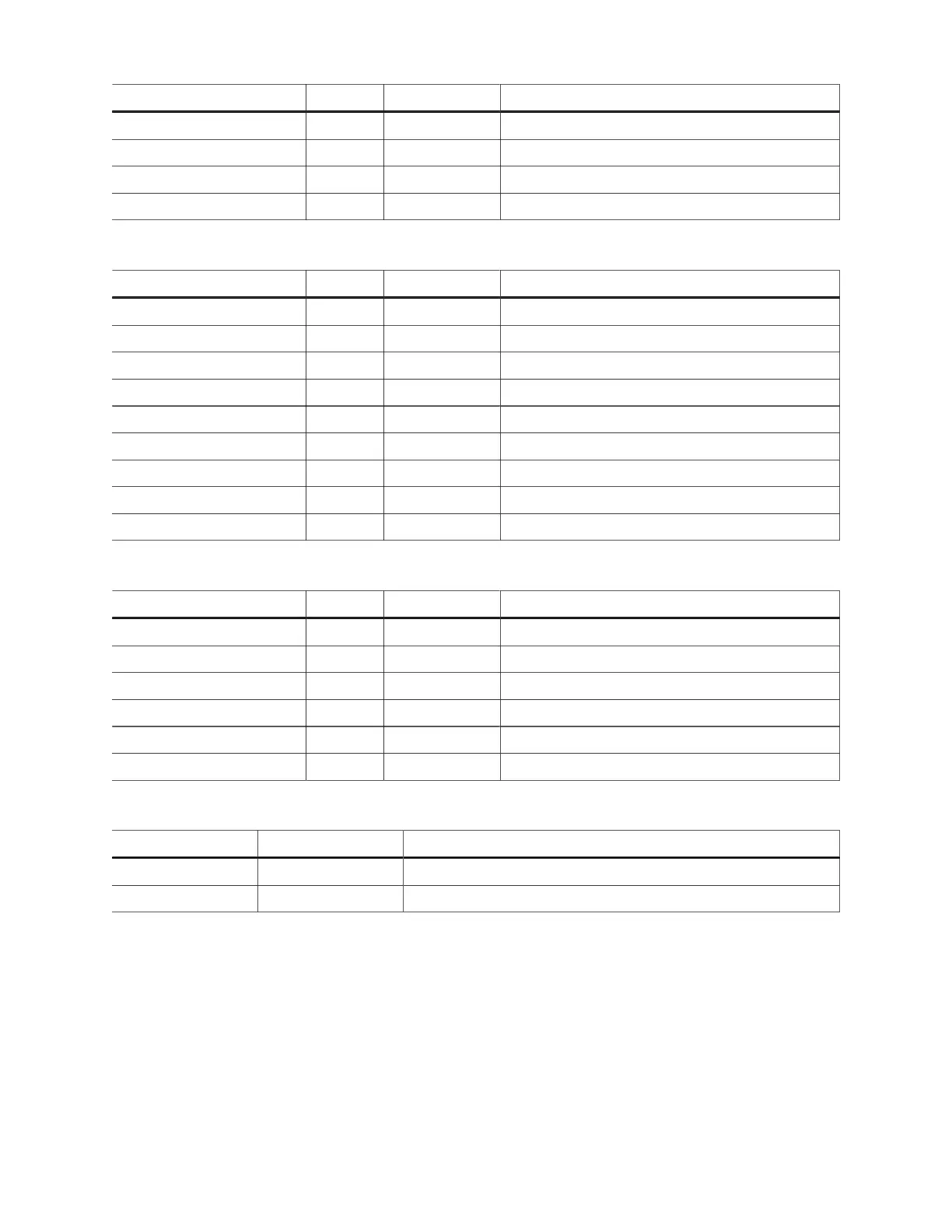

Signal Direction Clock Domain Notes

HS_LANn_SKEWCAL Input BYTE_CLKOUT HS Skew Calibration (Lane N).

HS_LANn_HIGHVALID Input BYTE_CLKOUT HS High Byte Valid (Lane N) for 16-bit mode.

HS_LANn_DATA [15:0] Input BYTE_CLKOUT HS Transmit Data (Lane N).

HS_LANn_READY Output BYTE_CLKOUT HS Transmit Ready (Lane N).

Table 65: MIPI TX D-PHY Low-Power Data Receive Mode Signals (Interface to FPGA Fabric)

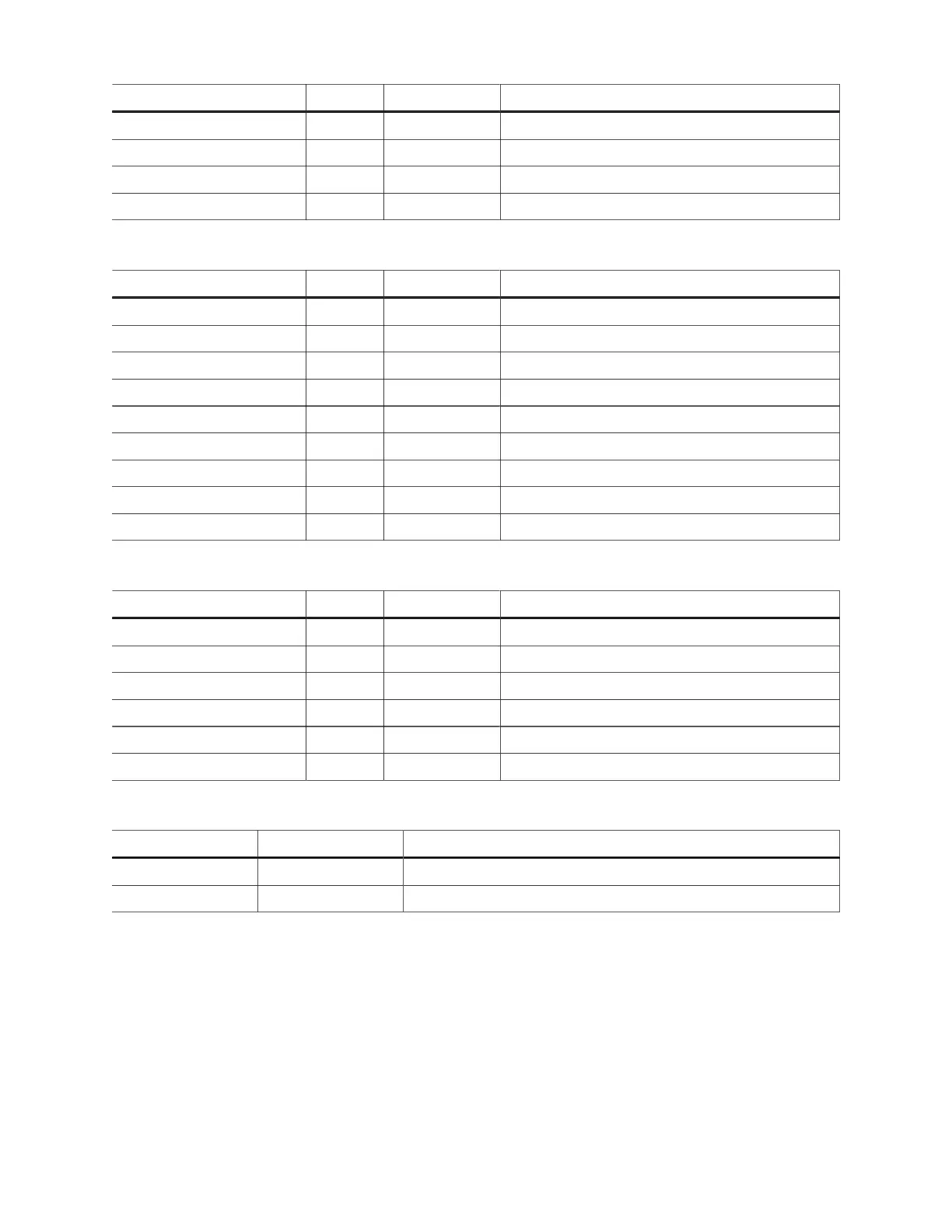

Signal Direction Clock Domain Notes

LPDT_TX_ENTER Input ESC_CLK Lane 0 Enter LPDT Mode.

LPDT_TX_VALID Input ESC_CLK Lane 0 LPDT Data Valid .

LPDT_TX_DATA [7:0] Input ESC_CLK Lane 0 LPDT Data Bus.

LPDT_TX_READY Output ESC_CLK Lane 0 LPDT Data Ready.

LDPT_RX_REQ Output ESC_CLKOUT Escape LP Data Receive Mode.

LPDT_RX_DATA [7:0] Output ESC_CLKOUT Escape Mode Receive Data.

LPDT_RX_VALID Output ESC_CLKOUT Escape Mode Receive Data Valid.

LDPT_RX_SYNC_ERROR Output N/A LPDT Data Sync Error.

ULPS_RX_ENTER Output ESC_CLKOUT Lane 0 entered ULPS mode.

Table 66: MIPI TX D-PHY ULP Sleep Mode (Interface to FPGA Fabric)

Signal Direction Clock Domain Notes

ULPS_CLK_ENTER Input ESC_CLK CLK0 to enter Ultra-Low Power State.

ULPS_CLK_EXIT Input ESC_CLK CLK0 to exit Ultra-Low Power State.

ULPS_CLK_ACTIVEN Output N/A Clock Lane in ULP State - Active Low (Clk 0).

ULPS_LANn_ENTER Input ESC_CLK Lane n to enter Ultra-Low Power State.

ULPS_LANn_EXIT Input ESC_CLK Lane n to exit Ultra-Low Power State.

ULPS_LANn_ACTIVEN Output N/A Data Lane in ULP State - Active Low (Lane N).

Table 67: MIPI TX D-PHY Pads

Pad Direction Description

TXDP[4:0] Bidirectional MIPI transceiver P pads.

TXDN[4:0] Bidirectional MIPI transceiver N pads.

www.efinixinc.com 116

Loading...

Loading...