Titanium Interfaces User Guide

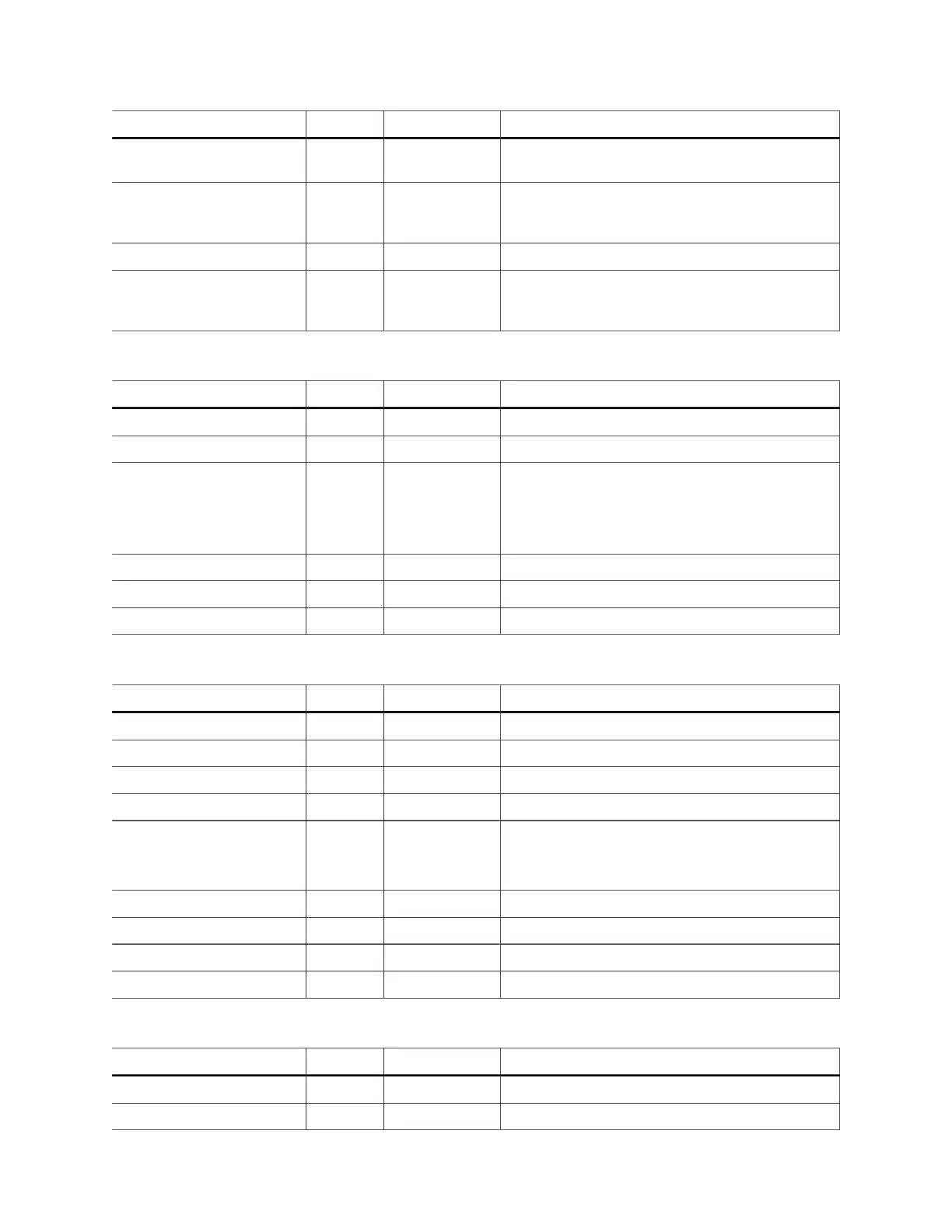

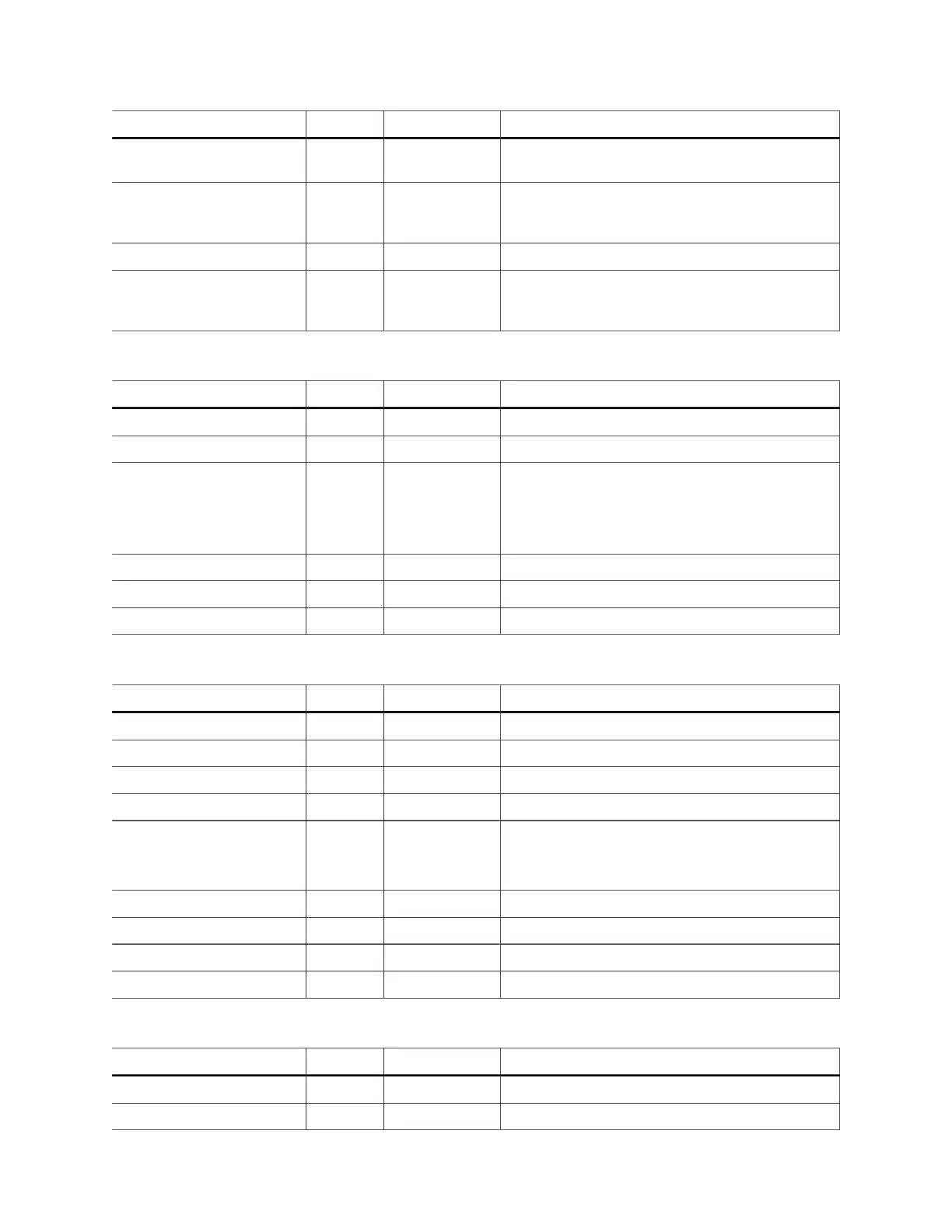

Table 61: MIPI TX D-PHY Clocks Signals (Interface to FPGA Fabric)

Signal Direction Clock Domain Notes

REF_CLK Input N/A Reference Clock. The clock must be between 12

MHz to 52 MHz.

ESC_CLK Input N/A Escape Mode Transmit Clock, used to generate

escape sequence. The clock must be less than 20

MHz.

ESC_CLKOUT Output N/A Escape Mode Receive Clock (lane 0 only)

BYTE_CLKOUT Output N/A HS Transmit Byte/Word Clock. This signal must be

1/8 or the bit-rate in normal 8-bit HS-PPI D-PHY

mode, or 1/16 of the bit-rate in 16-bit PHY mode.

Table 62: MIPI TX D-PHY Control and Status Signals (Interface to FPGA Fabric)

Signal Direction Clock Domain Notes

RESET Input N/A Reset. Disables PHY and reset the digital logic.

PLL_UNLOCK Output N/A PLL is in unlock state.

PLL_SSC_EN Input N/A (Optional) PLL SSC Enable:

Disabled: 1

Always enabled: 0

Driven by active signal for dynamic enable

STOPSTATE_CLK Output N/A Clock Lane in Stop State (Clk 0).

REQUESTESC_LANn Input ESC_CLK Escape Mode Transmit Request (Lane N).

STOPSTATE_LANn Output N/A Data Lane in Stop State (Lane N).

Table 63: MIPI TX D-PHY Lane 0 Control and Status Signals (Interface to FPGA Fabric)

Signal Direction Clock Domain Notes

TURNAROUND_REQ Input ESC_CLK Lane 0 Turnaround Request.

SEND_TRIGGER [3:0] Input ESC_CLK Lane 0 Send an Escape Mode Trigger Event.

RECV_TRIGGER[3:0] Output ESC_CLKOUT Lane 0 Received an Escape Mode Trigger Event.

FORCE_RX Input N/A Lane 0 Force into Receive Mode/Wait for Stop.

DIRECTION Output N/A Lane 0 Transmit/Receive Direction:

0: TX,

1: RX

ESC_CMD_ERROR Output N/A Lane 0 Escape Command Error.

LINE_STATE_ERROR Output N/A Lane 0 Line State Error.

CONTENTION_ERROR0 Output N/A Lane 0 Line Contention Detected (when driving 0).

CONTENTION_ERROR1 Output N/A Lane 0 Line Contention Detected (when driving 1).

Table 64: MIPI TX D-PHY High Speed Mode Signals (Interface to FPGA Fabric)

Signal Direction Clock Domain Notes

HS_CLK_REQUEST Input BYTE_CLKOUT HS Clock Request (Clk 0).

HS_LANn_REQUEST Input BYTE_CLKOUT HS Transmit Request and Data Valid (Lane 0-3).

www.efinixinc.com 115

Loading...

Loading...