Titanium Interfaces User Guide

MIPI TX D-PHY also interfaces with MIPI-associated protocol controllers via a standard

MIPI D-PHY PPI that supports the 8- or 16-bit high-speed receiving data bus.

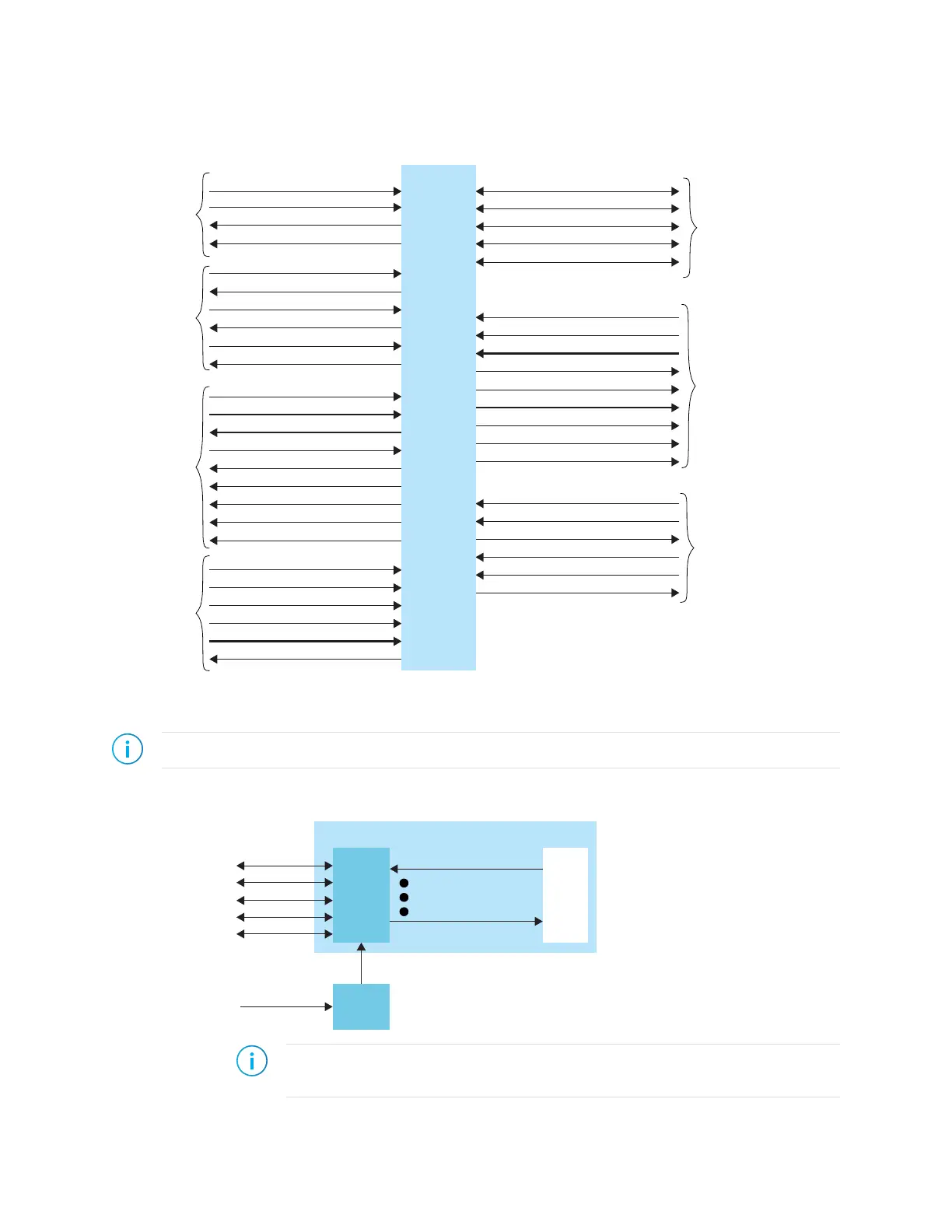

Figure 46: MIPI TX D-PHY x4 Block Diagram

TXDP/N4

TXDP/N3

TXDP/N2

TXDP/N1

TXDP/N0

Low-Power

Data Receive

Mode Signals

ULP Sleep

Mode Signals

REF_CLK

ESC_CLK

ESC_CLKOUT

BYTE_CLKOUT

RESET

PLL_UNLOCK

PLL_SSC_EN

STOPSTATE_CLK

REQUESTESC_LANn

STOPSTATE_LAN n

TURNAROUND_REQ

SEND_TRIGGER [3:0]

RECV_TRIGGER[3:0]

FORCE_RX

DIRECTION

ESC_CMD_ERROR

LINE_STATE_ERROR

CONTENTION_ERROR0

CONTENTION_ERROR1

HS_CLK_REQUEST

HS_LANn_REQUEST

HS_LANn_SKEWCAL

HS_LANn_HIGHVALID

HS_LANn_DATA [15:0]

HS_LANn_READY

LPDT_TX_ENTER

LPDT_TX_VALID

LPDT_TX_DATA [7:0]

LPDT_TX_READY

LDPT_RX_REQ

LPDT_RX_DATA [7:0]

LPDT_RX_VALID

LDPT_RX_SYNC_ERROR

ULPS_RX_ENTER

ULPS_CLK_ENTER

ULPS_CLK_EXIT

ULPS_CLK_ACTIVEN

ULPS_LANn_ENTER

ULPS_LANn_EXIT

ULPS_LANn_ACTIVEN

The MIPI TX D-PHY block requires an escape clock (ESC_CLK) for use when the MIPI

interface is in escape (low-power) mode, which runs up to 20 MHz.

Note: Efinix recommends that you set the escape clock frequency as close to 20 MHz as possible.

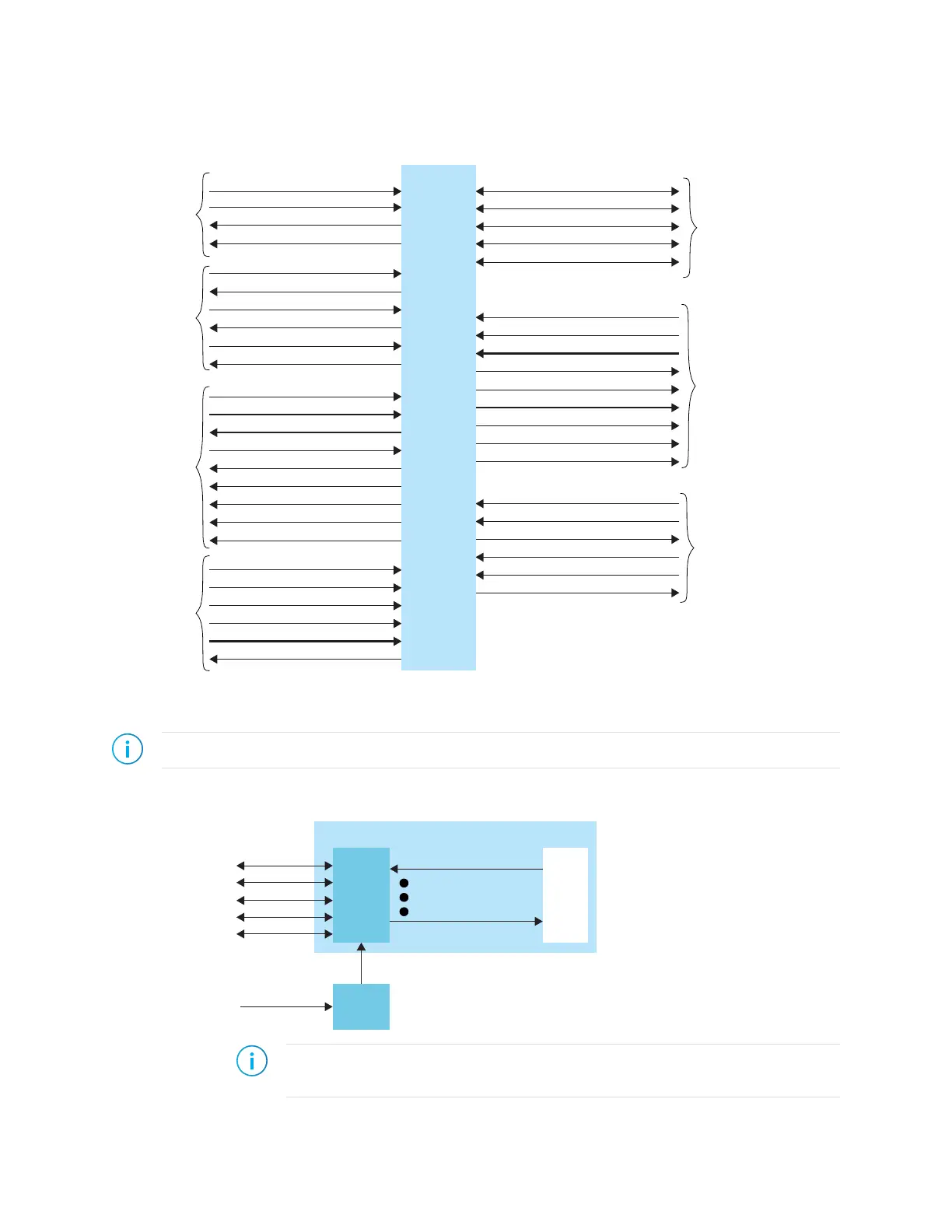

Figure 47: MIPI TX D-PHY Interface Block Diagram

TXDP/N4

TXDP/N3

TXDP/N2

TXDP/N1

TXDP/N0

Control, HS, LP,

and Status Signals

Note: GPIO block is the default reference clock source. However, the PLL and core

clock out can also be set as the reference clock source.

www.efinixinc.com 114

Loading...

Loading...