Titanium Interfaces User Guide

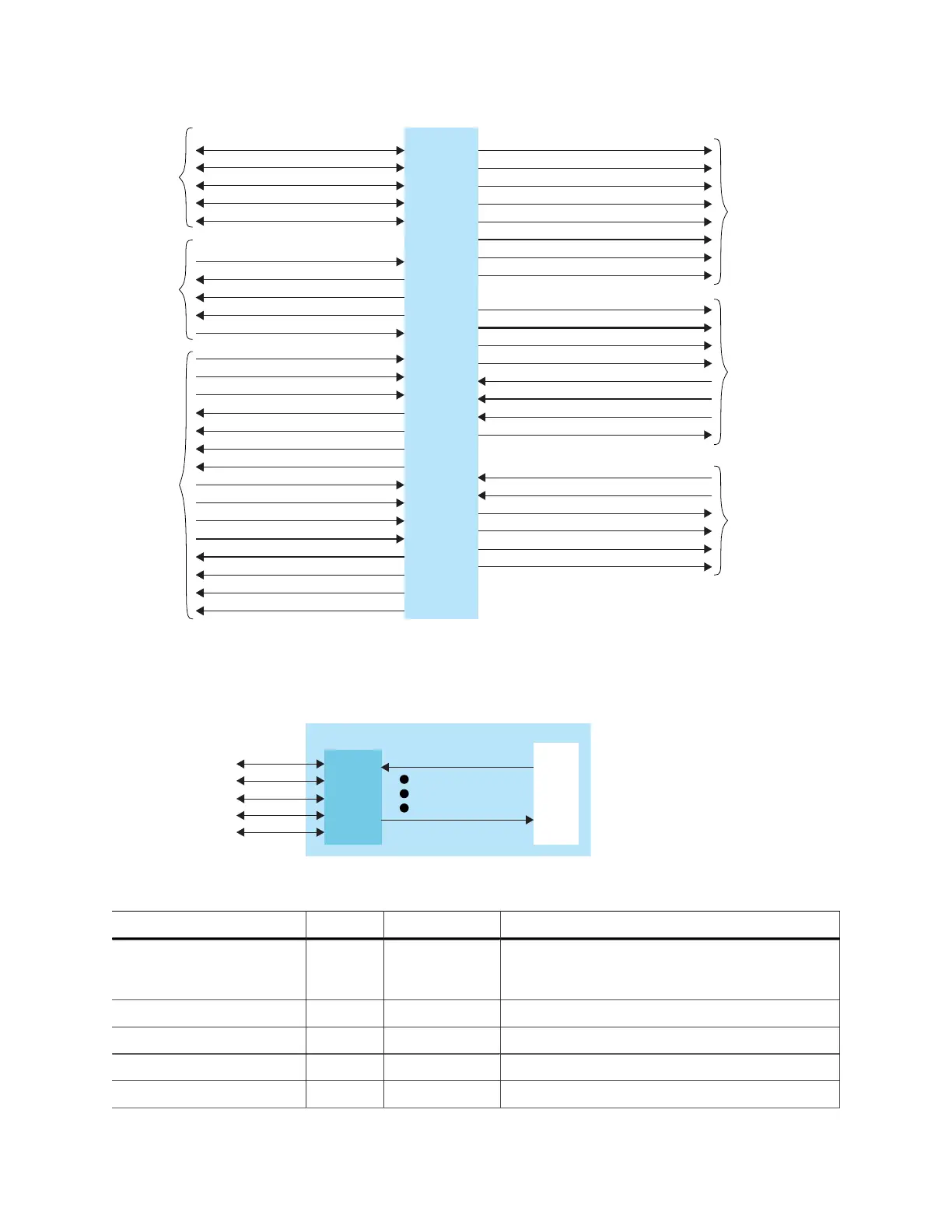

Figure 44: MIPI RX D-PHY x4 Block Diagram

RXDP/N4

RXDP/N3

RXDP/N2

RXDP/N1

RXDP/N0

MIPI RX

D-PHY

Block

High-Speed

Mode Signals

Low-Power

Data Receive

Mode Signals

CAL_CLK

BYTE_CLKOUT

LP_CLK

ESC_LANn_CLKOUT

ESC_CLK

RESET

RST0_N

RST1_N

STOPSTATE_CLK

STOPSTATE_LAN n

ESC_LANn_ERROR

LINESTATE_LAN n_ERROR

REQUEST_TX_ESC

TURNAROUND_REQ

FORCE_RX

SEND_TRIGGER [3:0]

RECV_TRIGGER [3:0]

DIRECTION

CONTENTION_ERROR0

CONTENTION_ERROR1

HS_CLK_ACTIVE

HS_LANn_ACTIVE

HS_LANn_VALID

HS_LANn_SYNC

HS_LANn_SKEWCAL

HS_LANn_DATA [15:0]

HS_LANn_SOT_ERR

HS_LANn_SOTSYNC_ERROR

LPDT_RX_ENTER

LPDT_RX_DATA [7:0]

LPDT_RX_VALID

LPDT_RX_SYNC_ERR

LPDT_TX_ENTER

LPDT_TX_DATA [7:0]

LDPT_TX_VALID

LPDT_TX_READY

ULPS_TX_ENTER

ULPS_TX_EXIT

ULPS_CLK_ENTER

ULPS_CLK_ACTIVEN

ULPS_LANn_ENTER

ULPS_LANn_ACTIVEN

ULP Sleep

Mode Signals

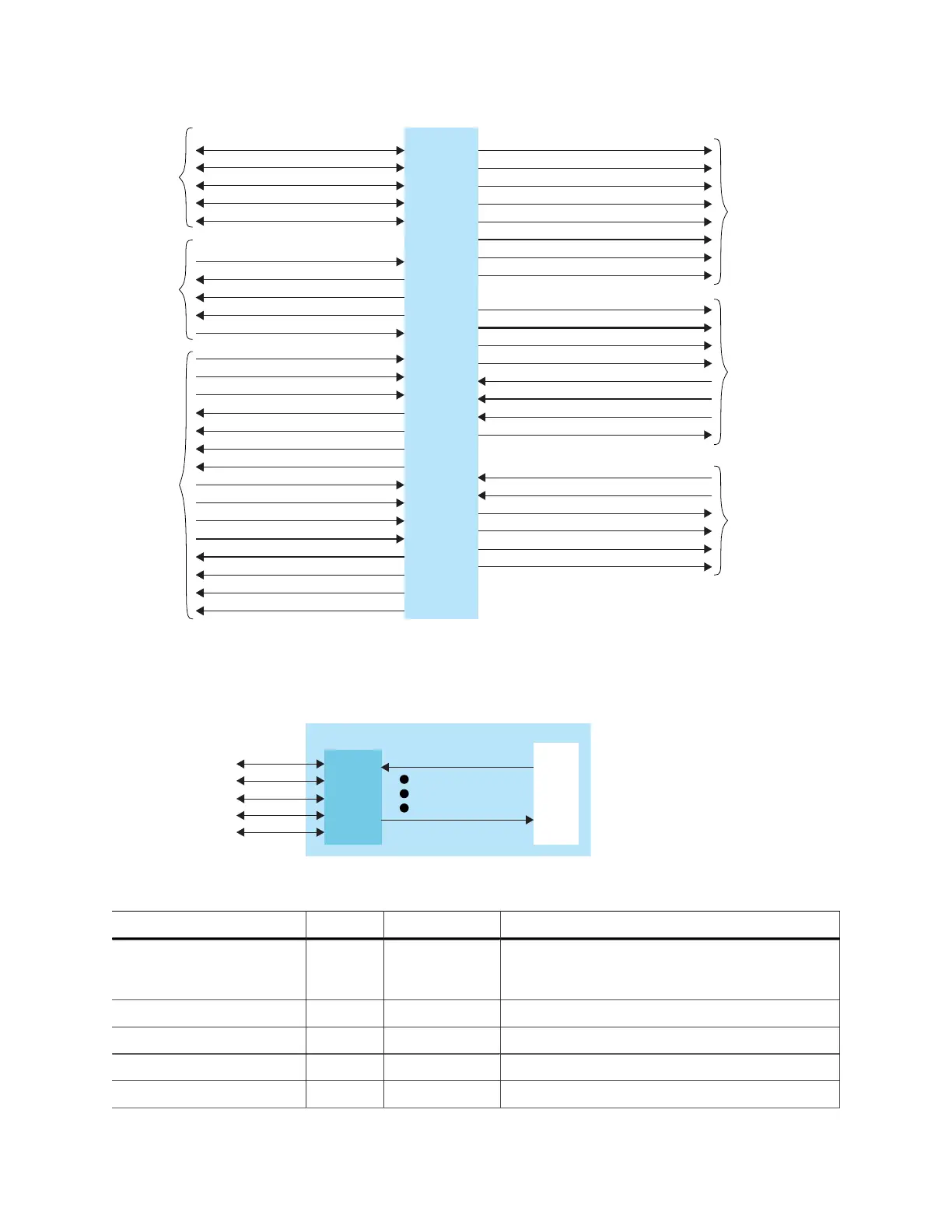

The status signals provide optional status and error information about the MIPI RX D-PHY

interface operation.

Figure 45: MIPI RX D-PHY Interface Block Diagram

MIPI

D-PHY

Block

Control, HS, LP,

and Status Signals

RXDP/N4

RXDP/N3

RXDP/N2

RXDP/N1

RXDP/N0

Table 55: MIPI RX D-PHY Clocks Signals (Interface to FPGA Fabric)

Signal Direction Clock Domain Notes

CAL_CLK Input N/A Configuration Clock (used for time counter and EQ

calibration). The clock must be between 80 MHz to

120 MHz.

BYTE_CLKOUT Output N/A HS Receive Byte/Word clock.

LP_CLK Output N/A Low Power State clock.

ESC_LANn_CLKOUT Output N/A Escape Mode Receive clock.

ESC_CLK Input N/A Escape Mode Transmit clock.

www.efinixinc.com 111

Loading...

Loading...