Titanium Interfaces User Guide

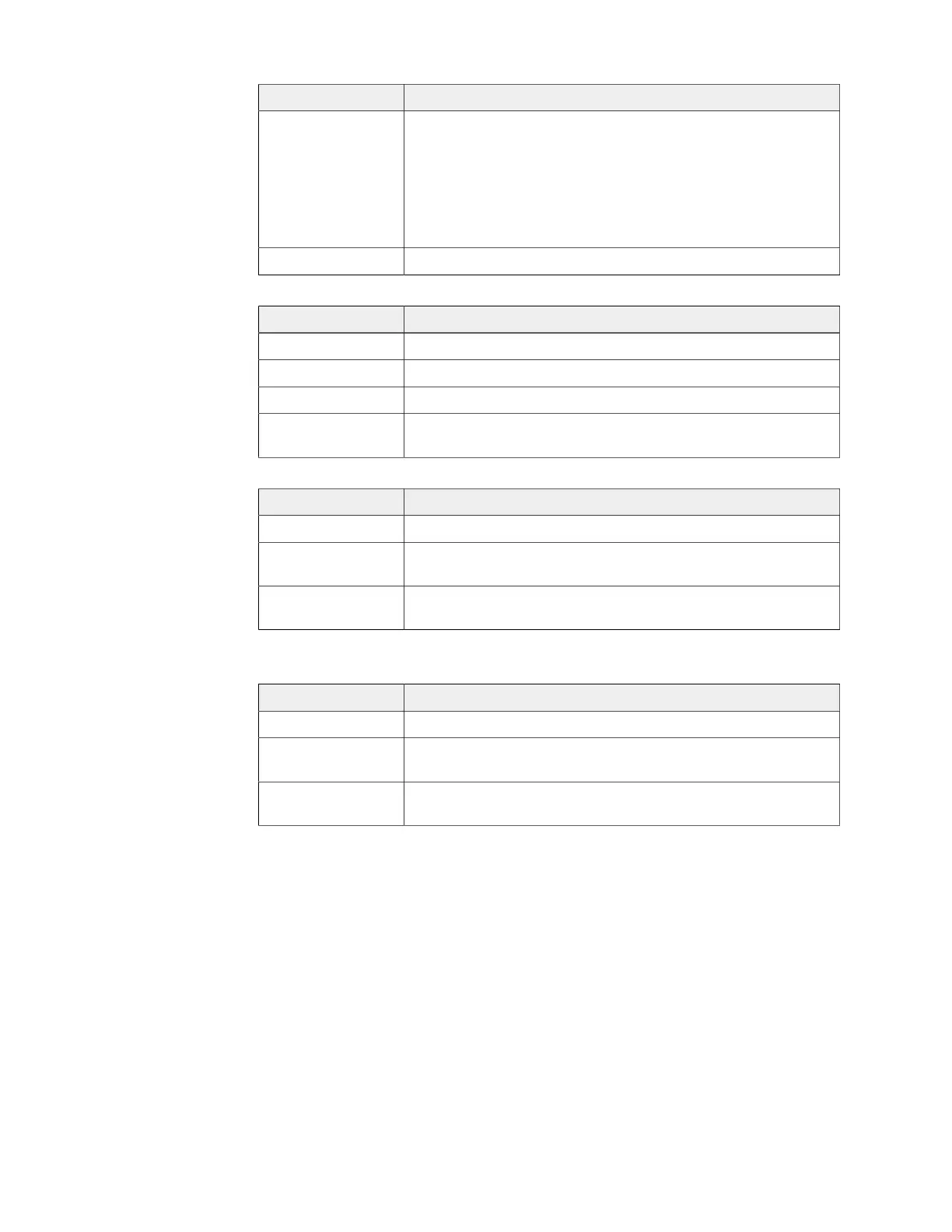

Option Description

FASTCLK_D—Frequency is the speed you are running the PHY,

phase shift 45.00°

FASTCLK_C—Frequency is the speed you are running the PHY,

phase shift 135.00°

For example, if the PHY is running at 1,000 Mbps, FASTCLK_D and

FASTCLK_C will run at half that 500 MHz (because it transfers data

on both clock edges), and SLOWCLK will run at 125 MHz.

Locked Pin Turn on

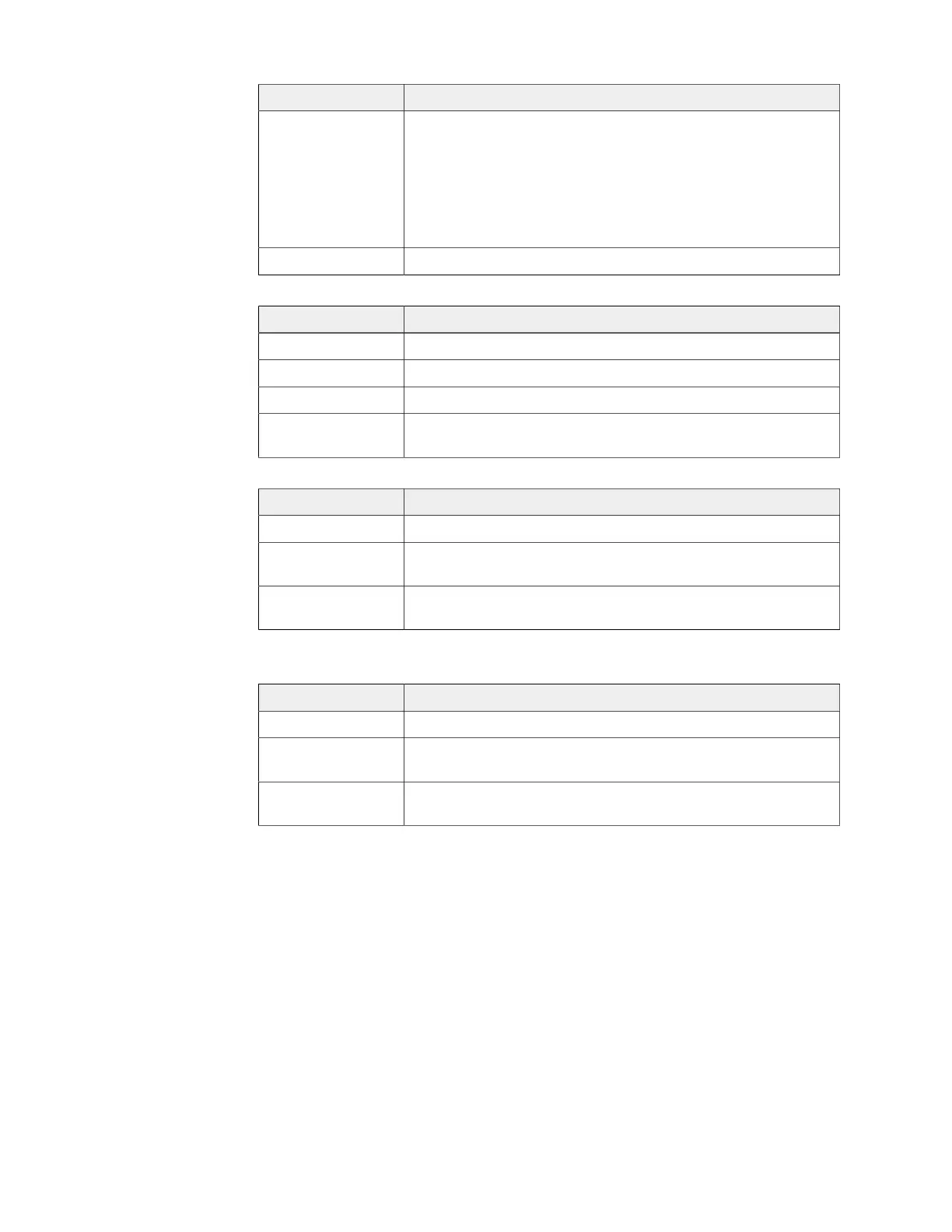

2. Add a GPIO block with these settings to provide the reference clock input to the PLL:

Option Description

Mode Input

Pin Name Any

Connection Type pll_clkin

GPIO Resource Assign the dedicated PLL_CLKIN pin that corresponds to the PLL

you chose.

3. Add MIPI TX Lane block with these settings:

Option Description

Mode data lane

Parallel Clock

Pin Name

Name you are using for SLOWCLK.

Serial Clock

Pin Name

Name you are using for FASTCLK_D.

4. Repeat step 3 for each MIPI TX data lane you want to implement.

5. Add another MIPI TX Lane block for the clock lane:

Option Description

Mode clock lane

Parallel Clock

Pin Name

Name you are using for SLOWCLK.

Serial Clock

Pin Name

Name you are using for FASTCLK_C.

6. Implement the rest of the MIPI TX interface in RTL using a MIPI TX IP core (CSI-2, D-

PHY, or DSI). Refer to the user guide for the IP core for instructions.

www.efinixinc.com 105

Loading...

Loading...