Titanium Interfaces User Guide

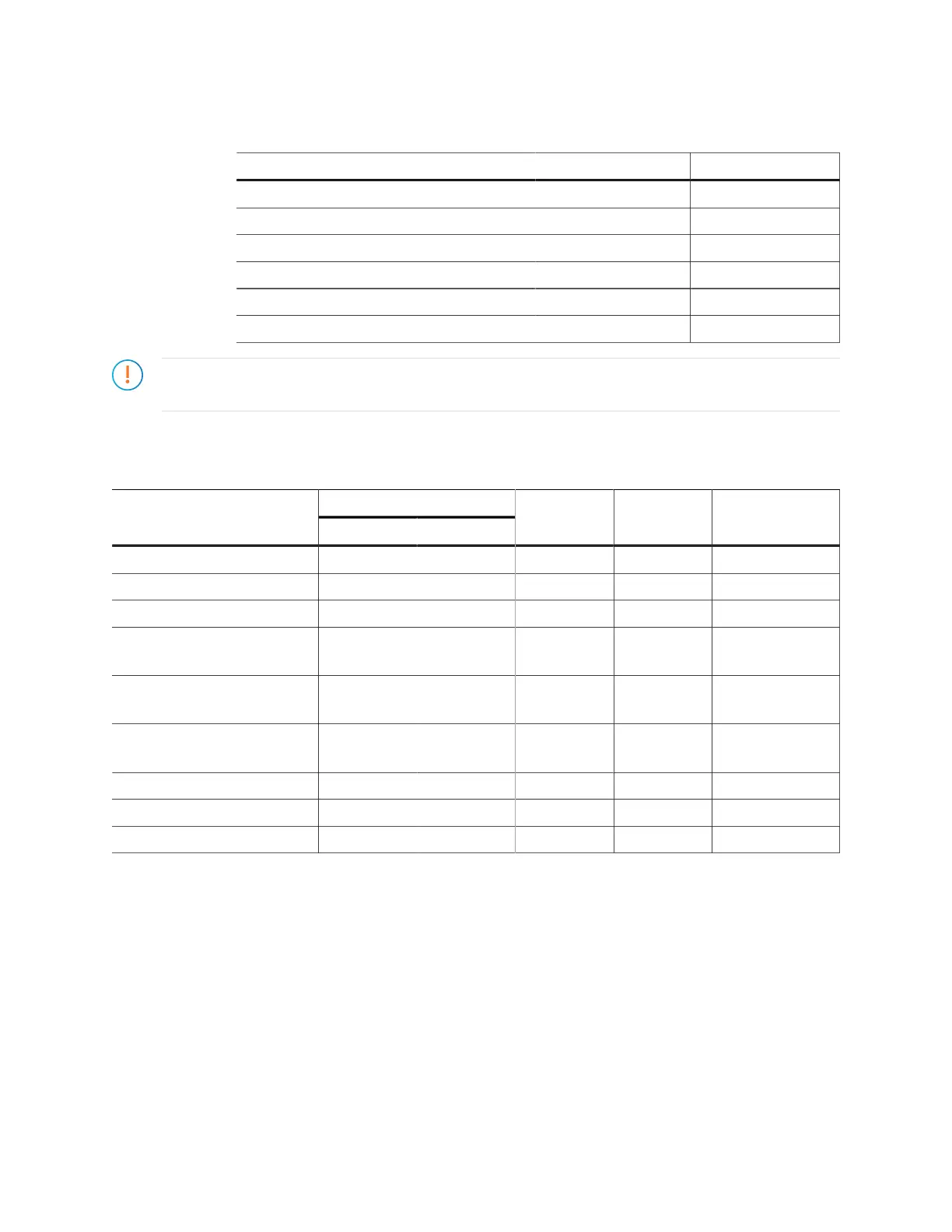

The HVIO supports the following I/O standards.

Table 26: HVIO Supported Standards

Standard VCCIO33 (V) When Configured As

LVTTL 3.3 V 3.3 GPIO

LVTTL 3.0 V 3.0 GPIO

LVCMOS 3.3 V 3.3 GPIO

LVCMOS 3.0 V 3.0 GPIO

LVCMOS 2.5 V 2.5 GPIO

LVCMOS 1.8 V 1.8 GPIO

Important: Efinix recommends that you limit the number of 3.0/3.3 V HVIO as I/O or output to 6 per bank

to avoid switching noise. The Efinity

®

software issues a warning if you exceed the recommended limit.

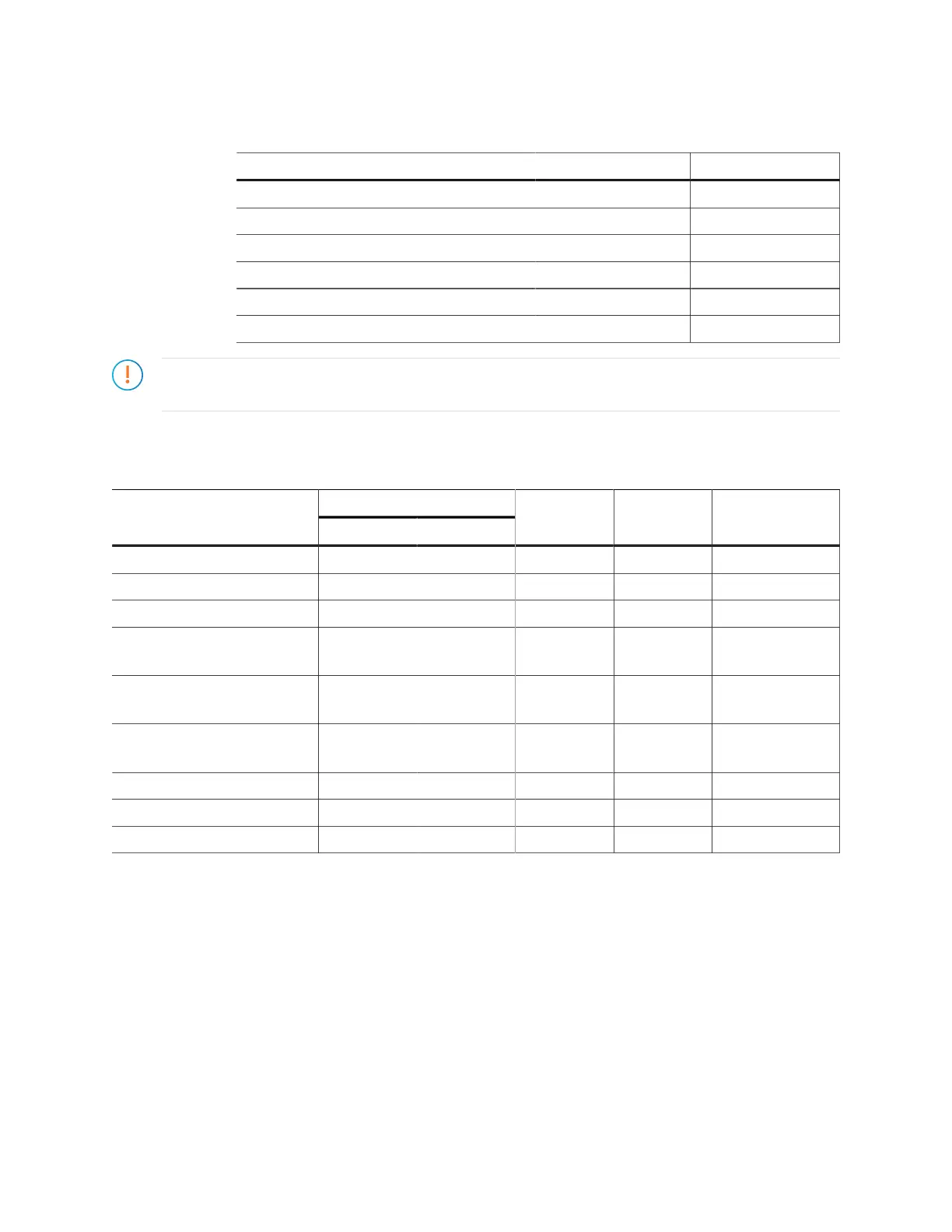

The HSIO supports the following I/O standards.

Table 27: HSIO Supported I/O Standards

VCCIO (V)Standard

TX RX

VCCAUX (V) VREF (V) When

Configured As

LVCMOS 1.8 V 1.8 1.8 1.8 – GPIO

LVCMOS 1.5 V 1.5 1.5 1.8 – GPIO

LVCMOS 1.2 V 1.2 1.2 1.8 – GPIO

HSTL/Differential HSTL 1.8 V

SSTL/Differential SSTL 1.8 V

1.8 1.8 1.8 0.9 GPIO

HSTL/Differential HSTL 1.5 V

SSTL/Differential SSTL 1.5 V

1.5 1.5, 1.8 1.8 0.75 GPIO

HSTL/Differential HSTL 1.2 V

SSTL/Differential SSTL 1.2 V

1.2 1.2, 1.5, 1.8 1.8 0.6 GPIO

LVDS/RSDS/mini-LVDS 1.8 1.8 1.8 – LVDS

Sub-LVDS 1.8 1.5, 1.8 1.8 – LVDS

MIPI Lane I/O /SLVS 1.2 1.2 1.8 – MIPI Lane

The differential receivers are powered by VCCAUX, which gives you the flexibility to

choose the VCCIO you want to use.

www.efinixinc.com 40

Loading...

Loading...