Titanium Interfaces User Guide

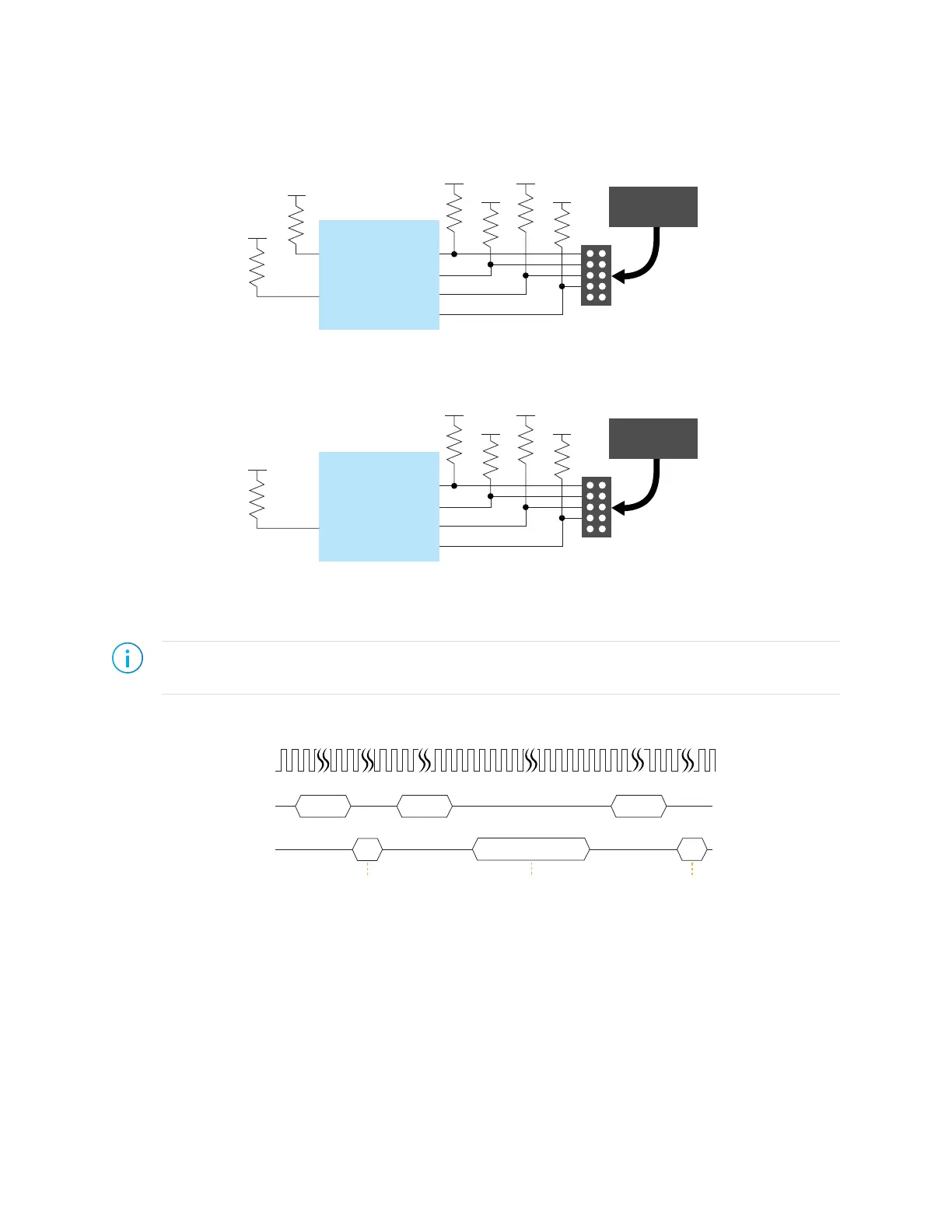

Connect the FPGA pins as shown in the following diagrams.

Figure 31: JTAG Programming (Packages without MIPI D-PHY Block)

See Resistors in Configuration Circuitry for the resistor values.

FPGA

JTAG Header

JTAG

Cable/Module

TMS

TCK

TDO

TDI

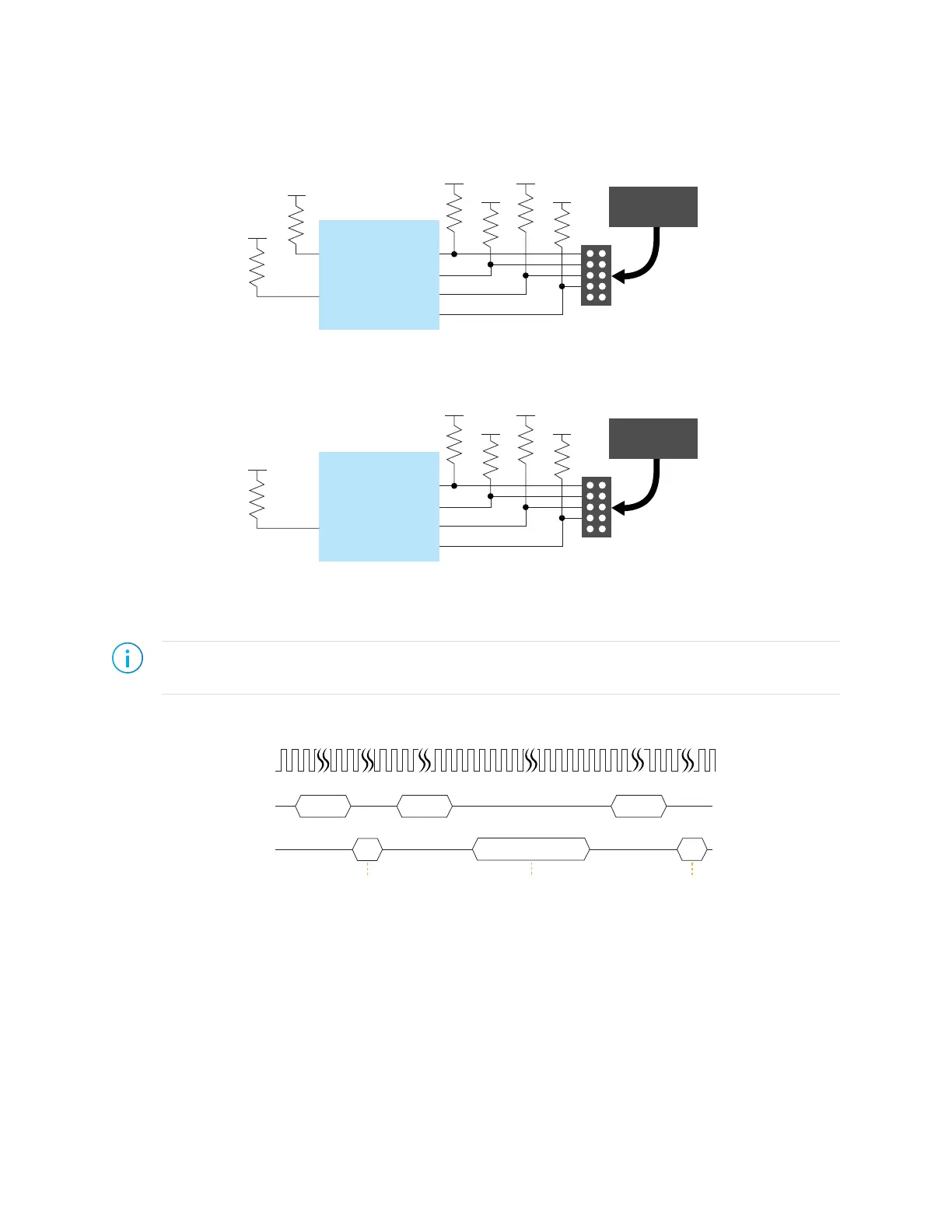

Figure 32: JTAG Programming (Packages with MIPI D-PHY Block)

See Resistors in Configuration Circuitry for the resistor values.

When configuration ends, the JTAG host issues the ENTERUSER instruction to the FPGA.

After CDONE goes high and the FPGA receives the ENTERUSER instruction, the FPGA

waits for t

USER

to elapse, and then it goes into user mode.

Note: The FPGA may go into user mode before t

USER

has elapsed. Therefore, you should keep the system

interface with the FPGA in reset until t

USER

has elapsed.

Figure 33: JTAG Programming Waveform

Shift DR Capture IR

Shift In

Configuration Data

Program

Instruction

ENTERUSER

Instruction

www.efinixinc.com 91

Loading...

Loading...