MOTOROLA M68020 USER’S MANUAL 6- 27

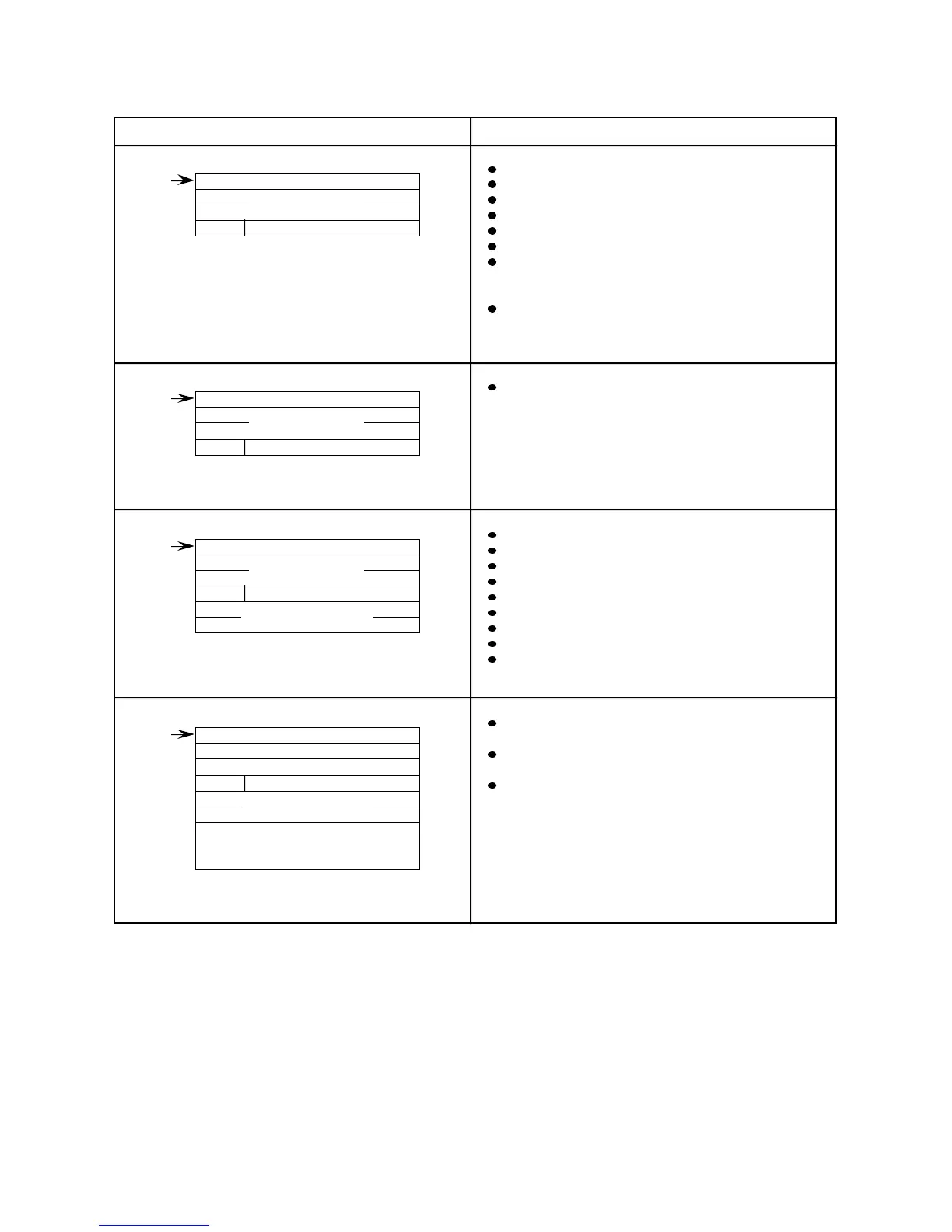

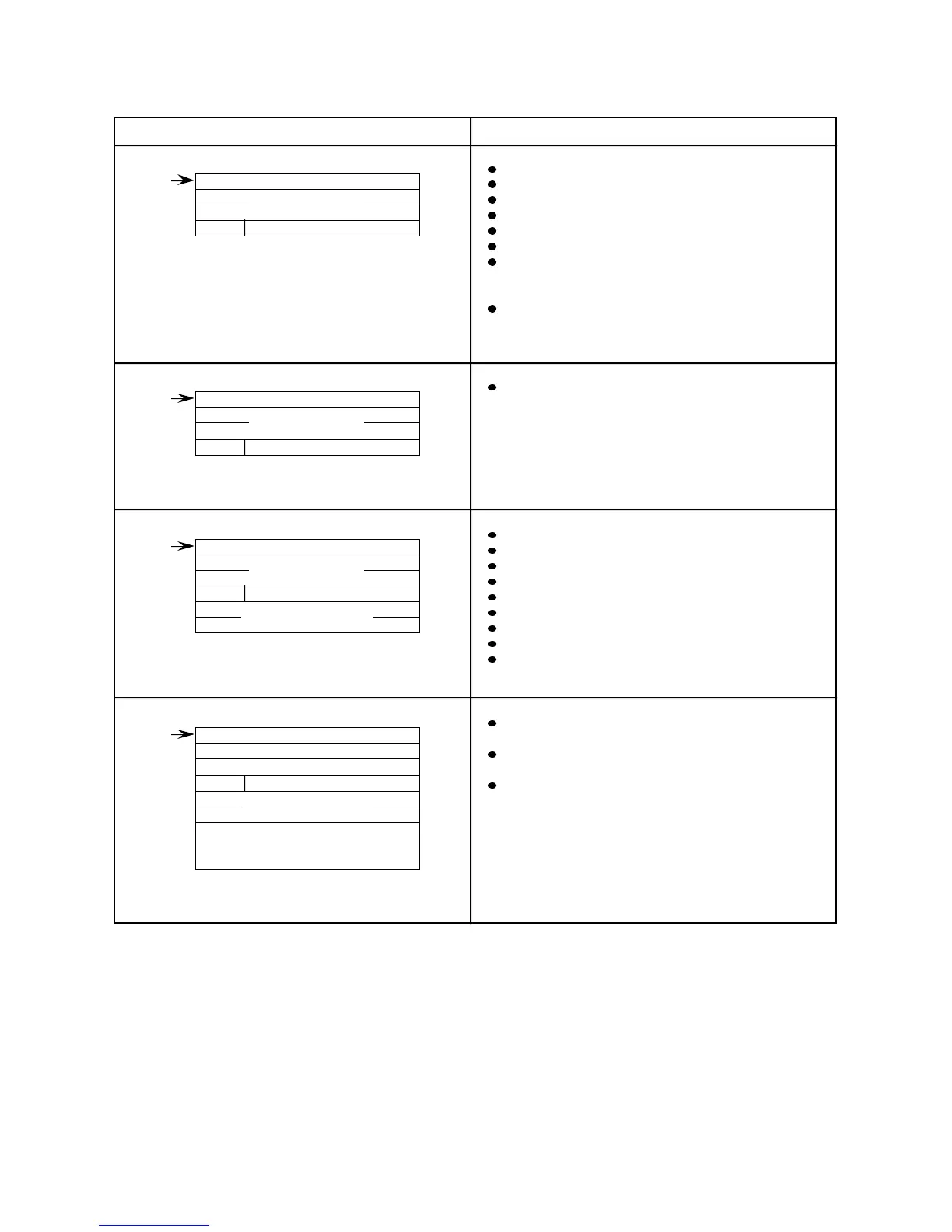

Table 6-5. Exception Stack Frames

SIX-WORD

STACK FRAME — FORMAT $2

Exception Types (Stacked PC Points to)Stack Frames

Interrupt

Format Error

TRAP #N

Illegal Instruction

A-Line Instruction

F-Line Instruction

Privilege Violation

Coprocessor

Preinstruction

[Next instruction]

[RTE or cpRESTORE instruction

[NEXT instruction]

[Illegal instruction]

[A-line instruction]

[F-line instruction]

[First word of instruction causing

Privilege Violation]

[Opword of instruction that

returned the 'take preinstruction'

primitive]

THROWAWAY FOUR-WORD

STACK FRAME — FORMAT $1

Created on

Interrupt Stack

during interrupt

exception processing

when transition from

master state to

interrupt state occurs

[Next instruction — same as on

master stack]

STATUS REGISTER

15 0

PROGRAM COUNTER

VECTOR OFFSET0010

SP

+$06

+$02

CHK

CHK2

cpTRAPcc

TRAPcc

TRAPPV

Trace

Zero Divide

MMU Configuration

Coprocessor

Postinstruction

[Next instruction for all these

exceptions]

INSTRUCTION ADDRESS

is the address of the instruction

that caused the exception

INSTRUCTION ADDRESS

+$08

STATUS REGISTER

15 0

PROGRAM COUNTER

VECTOR OFFSET1001

SP

+$06

+$02

Coprocessor

Midinstruction

Main-Detected

Protocol Violation

Interrupt Detected

During Coprocessor

Instruction

(supported with 'null

come again with

interrupts allowed'

primitive)

INSTRUCTION ADDRESS+$08

COPROCESSOR MIDINSTRUCTION

STACK FRAME (10 WORDS) — FORMAT $9

INTERNAL REGISTERS,

4 WORDS

+$0C

+$12

[Next word to be fetched from

instruction stream for all these

exceptions]

INSTRUCTION ADDRESS

is the address of the instruction

that caused the exception

FOUR-WORD STACK FRAME — FORMAT $0

STATUS REGISTER

15 0

PROGRAM COUNTER

VECTOR OFFSET0000

SP

+$06

+$02

STATUS REGISTER

15 0

PROGRAM COUNTER

VECTOR OFFSET000

1

SP

+$06

+$02

Loading...

Loading...