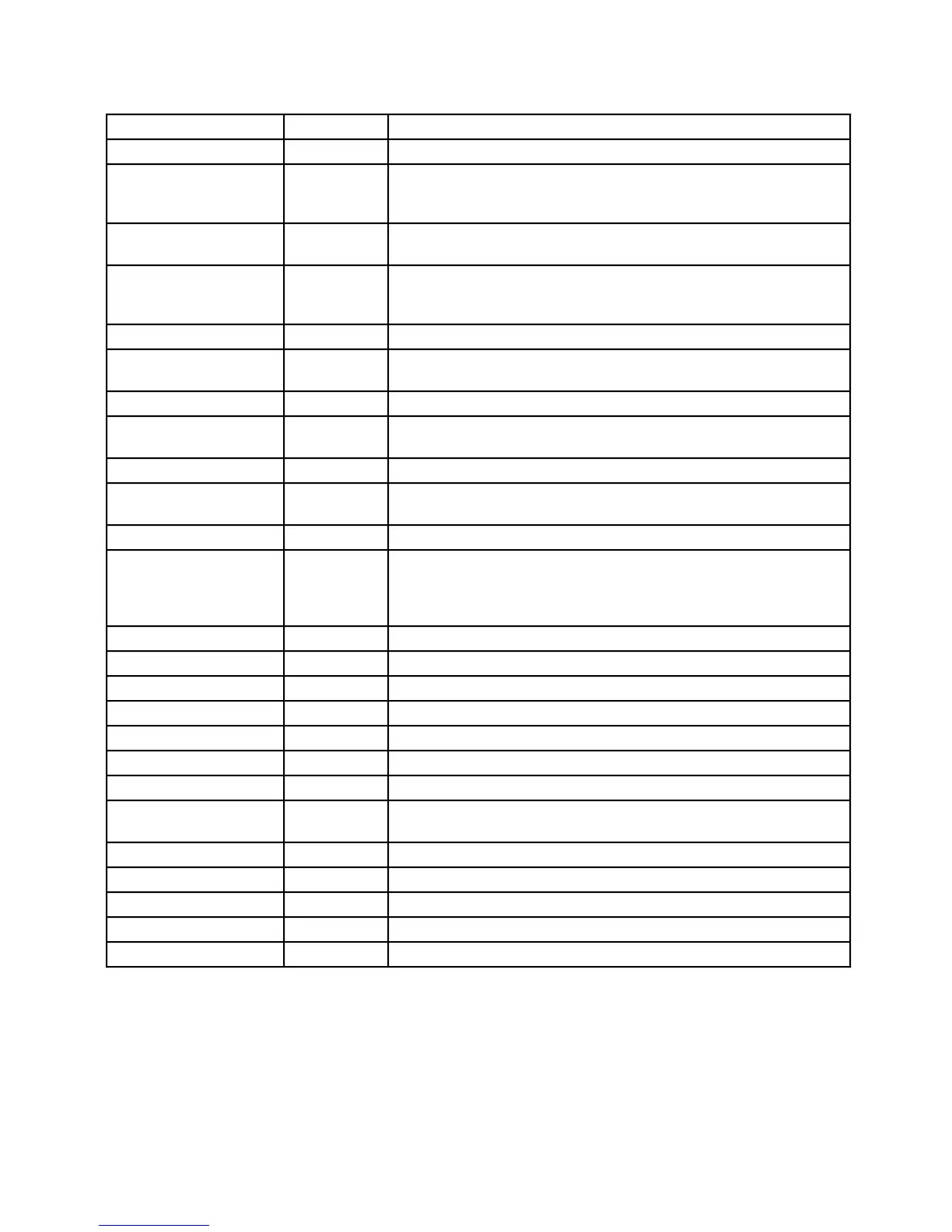

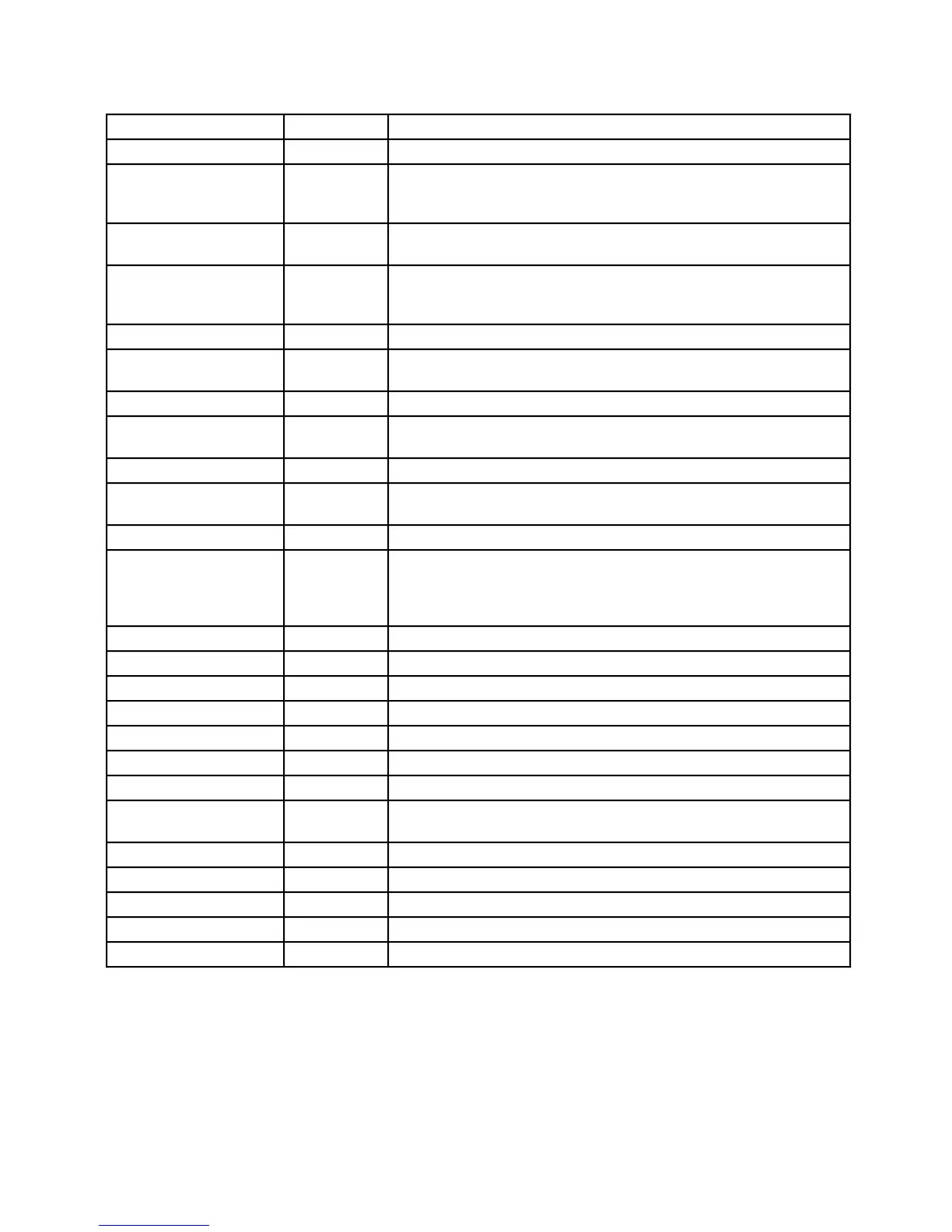

MOTOROLA M68020 USER’S MANUAL 3- 3

Table 3-1. Signal Index

Signal Name Mnemonic Function

Function Codes FC2–FC0 3-bit function code used to identify the address space of each bus cycle.

Address Bus

MC68020

MC68EC020

A31–A0

A23–A0

32-bit address bus

24-bit address bus

Data Bus D31–D0 32-bit data bus used to transfer 8, 16, 24, or 32 bits of data per bus

cycle.

Size SIZ1, SIZ0 Indicates the number of bytes remaining to be transferred for this cycle.

These signals, together with A1 and A0, define the active sections of the

data bus.

*External Cycle Start ECS Provides an indication that a bus cycle is beginning.

*Operand Cycle Start OCS Identical operation to that of ECS except that OCS is asserted only during

the first bus cycle of an operand transfer.

Read/Write R/W Defines the bus transfer as a processor read or write.

Read-Modify-Write Cycle RMC Provides an indicator that the current bus cycle is part of an indivisible

read-modify-write operation.

Address Strobe AS Indicates that a valid address is on the bus.

Data Strobe DS Indicates that valid data is to be placed on the data bus by an external

device or has been placed on the data bus by the MC68020/EC020.

*Data Buffer Enable DBEN Provides an enable signal for external data buffers.

Data Transfer and Size

Acknowledge

DSACK1,

DSACK0

Bus response signals that indicate the requested data transfer operation

has completed. In addition, these two lines indicate the size of the

external bus port on a cycle-by-cycle basis and are used for

asynchronous transfers.

Interrupt Priority Level IPL2–IPL0 Provides an encoded interrupt level to the processor.

*Interrupt Pending IPEND Indicates that an interrupt is pending.

Autovector AVEC Requests an autovector during an interrupt acknowledge cycle.

Bus Request BR Indicates that an external device requires bus mastership.

Bus Grant BG Indicates that an external device may assume bus mastership.

*Bus Grant Acknowledge BGACK Indicates that an external device has assumed bus mastership.

Reset RESET System reset.

Halt HALT Indicates that the processor should suspend bus activity or that the

processor has halted due to a double bus fault.

Bus Error BERR Indicates that an erroneous bus operation is being attempted.

Cache Disable CDIS Statically disables the on-chip cache to assist emulator support.

Clock CLK Clock input to the processor.

Power Supply V

CC

Power supply.

Ground GND Ground connection.

*This signal is implemented in the MC68020 and not implemented in the MC68EC020.

Loading...

Loading...