MOTOROLA M68020 USER’S MANUAL 7- 27

7.3.7 Condition CIR

The main processor initiates a conditional category instruction by writing the condition

selector to bits 5–0 of the 16-bit condition CIR. Bits 15–6 are undefined and reserved by

Motorola. The offset from the base address of the CIR set for the condition CIR is $0E.

Figure 7-20 shows the format of the condition CIR.

15

(UNDEFINED, RESERVED)

CONDITION SELECTOR

Figure 7-20. Condition CIR Format

7.3.8 Operand CIR

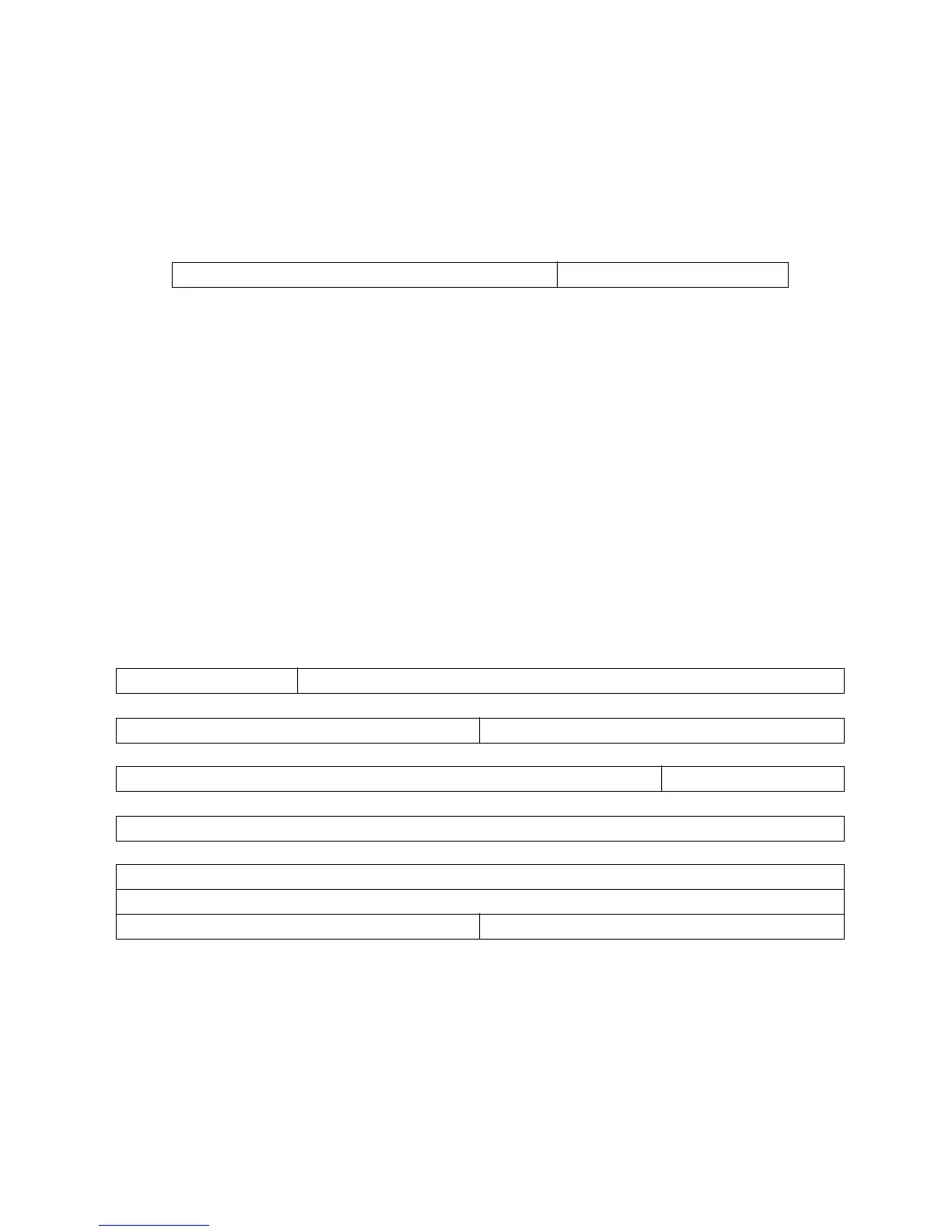

When the coprocessor requests the transfer of an operand, the main processor performs

the transfer by reading from or writing to the 32-bit operand CIR. The offset from the base

address of the CIR set for the operand CIR is $10.

The MC68020/EC020 aligns all operands transferred to and from the operand CIR to the

most significant byte of this CIR. The processor performs a sequence of long-word

transfers to read or write any operand larger than four bytes. If the operand size is not a

multiple of four bytes, the portion remaining after the initial long-word transfer is aligned to

the most significant byte of the operand CIR. Figure 7-21 shows the operand alignment

used by the MC68020/EC020 when accessing the operand CIR.

0

O TRANSFE

ORD OPERAN

HREE-BYTE OPERAN

ONG-WORD OPERAN

NO TRANSFER

NO TRANSFER

NO TRANSFER

PERAN

YTE

EN

YTE OPERAN

Figure 7-21. Operand Alignment for Operand CIR Accesses

Loading...

Loading...