8- 34 M68020 USER’S MANUAL MOTOROLA

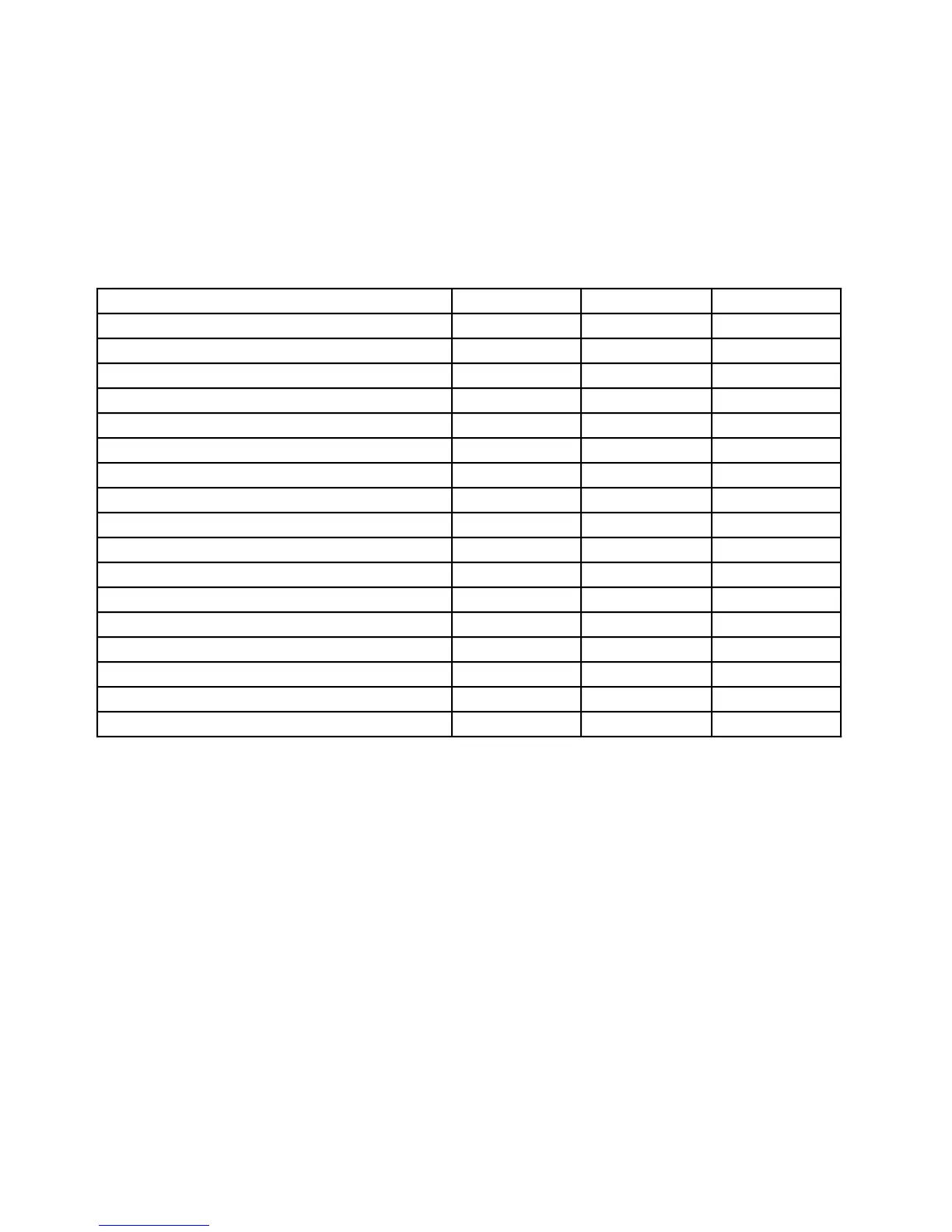

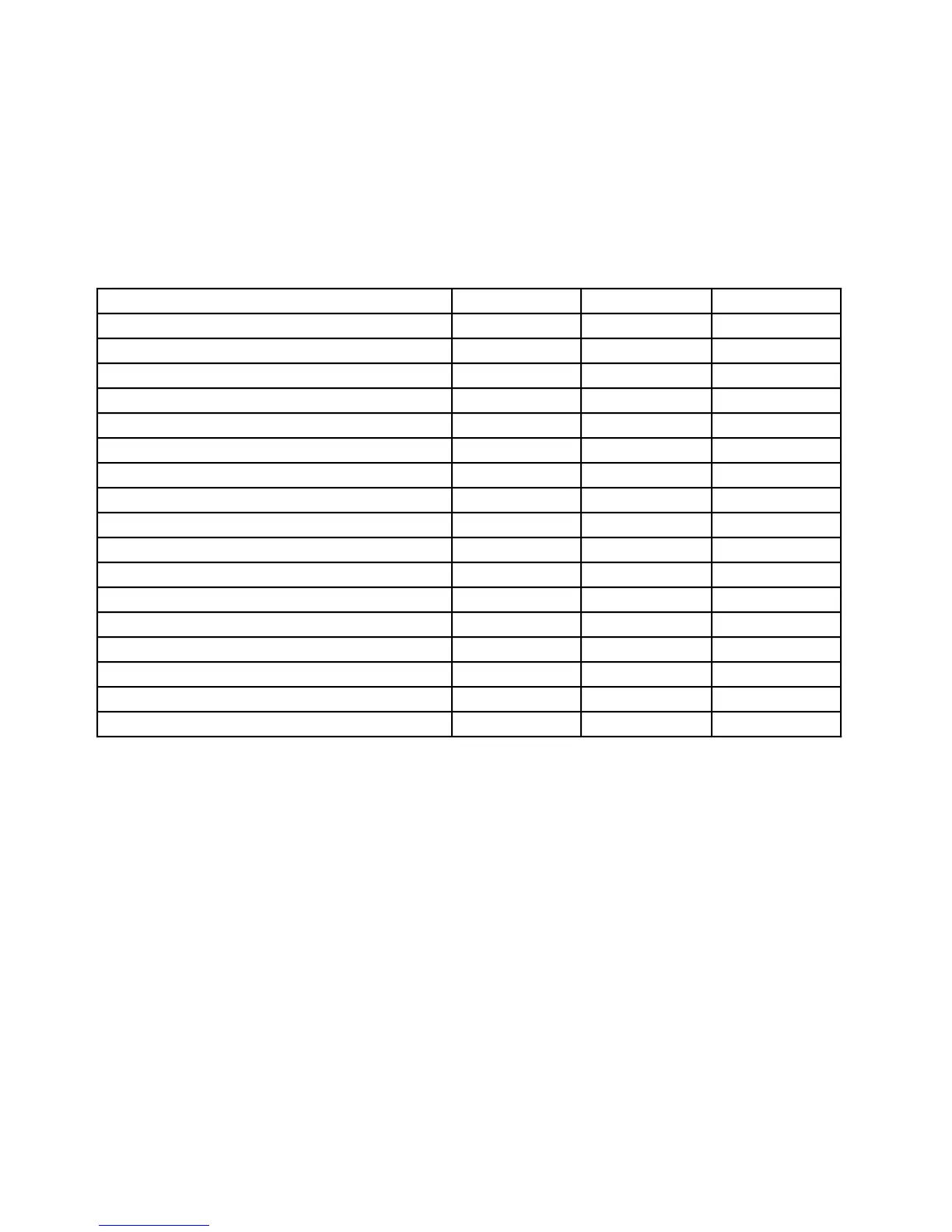

8.2.12 Shift/Rotate Instructions

The shift/rotate instructions table indicates the number of clock periods needed for the

processor to perform the specified operation on the given addressing mode. Footnotes

indicate when it is necessary to add another table entry to calculate the total effective

execution time for the instruction. The number of bits shifted does not affect execution

time. The total number of clock cycles is outside the parentheses, the number of read,

prefetch, and write cycles is given inside the parentheses as (r/p/w). These cycles are

included in the total clock cycle number.

Instruction Best Case Cache Case Worst Case

LSL Dn (Static) 1(0/0/0) 4(0/0/0) 4(0/1/0)

LSR Dn (Static) 1(0/0/0) 4(0/0/0) 4(0/1/0)

LSL Dn (Dynamic) 3(0/0/0) 6(0/0/0) 6(0/1/0)

LSR Dn (Dynamic) 3(0/0/0) 6(0/0/0) 6(0/1/0)

* LSL Mem by 1 5(0/0/1) 5(0/0/1) 6(0/1/1)

* LSR Mem by 1 5(0/0/1) 5(0/0/1) 6(0/1/1)

ASL Dn 5(0/0/0) 8(0/0/0) 8(0/1/0)

ASR Dn 3(0/0/0) 6(0/0/0) 6(0/1/0)

* ASL Mem by 1 6(0/0/1) 6(0/0/1) 7(0/1/1)

* ASR Mem by 1 5(0/0/1) 5(0/0/1) 6(0/1/1)

ROL Dn 5(0/0/0) 8(0/0/0) 8(0/1/0)

ROR Dn 5(0/0/0) 8(0/0/0) 8(0/1/0)

* ROL Mem by 1 7(0/0/1) 7(0/0/1) 7(0/1/1)

* ROR Mem by 1 7(0/0/1) 7(0/0/1) 7(0/1/1)

ROXL Dn 9(0/0/0) 12(0/0/0) 12(0/1/0)

ROXR Dn 9(0/0/0) 12(0/0/0) 12(0/1/0)

* ROXd Mem by 1 5(0/0/1) 5(0/0/1) 6(0/1/1)

*Add Fetch Effective Address Time

d—Direction of Shift/Rotate, L or R

Loading...

Loading...