7- 48 M68020 USER’S MANUAL MOTOROLA

which instruction the coprocessor was executing when the exception occurred. A

coprocessor can record the instruction address by setting PC = 1 in one of the primitives it

uses before releasing the main processor.

7.4.19 Take Midinstruction Exception Primitive

The take midinstruction exception primitive initiates exception processing using a

coprocessor-supplied exception vector number and the midinstruction exception stack

frame format. This primitive applies to general and conditional category instructions.

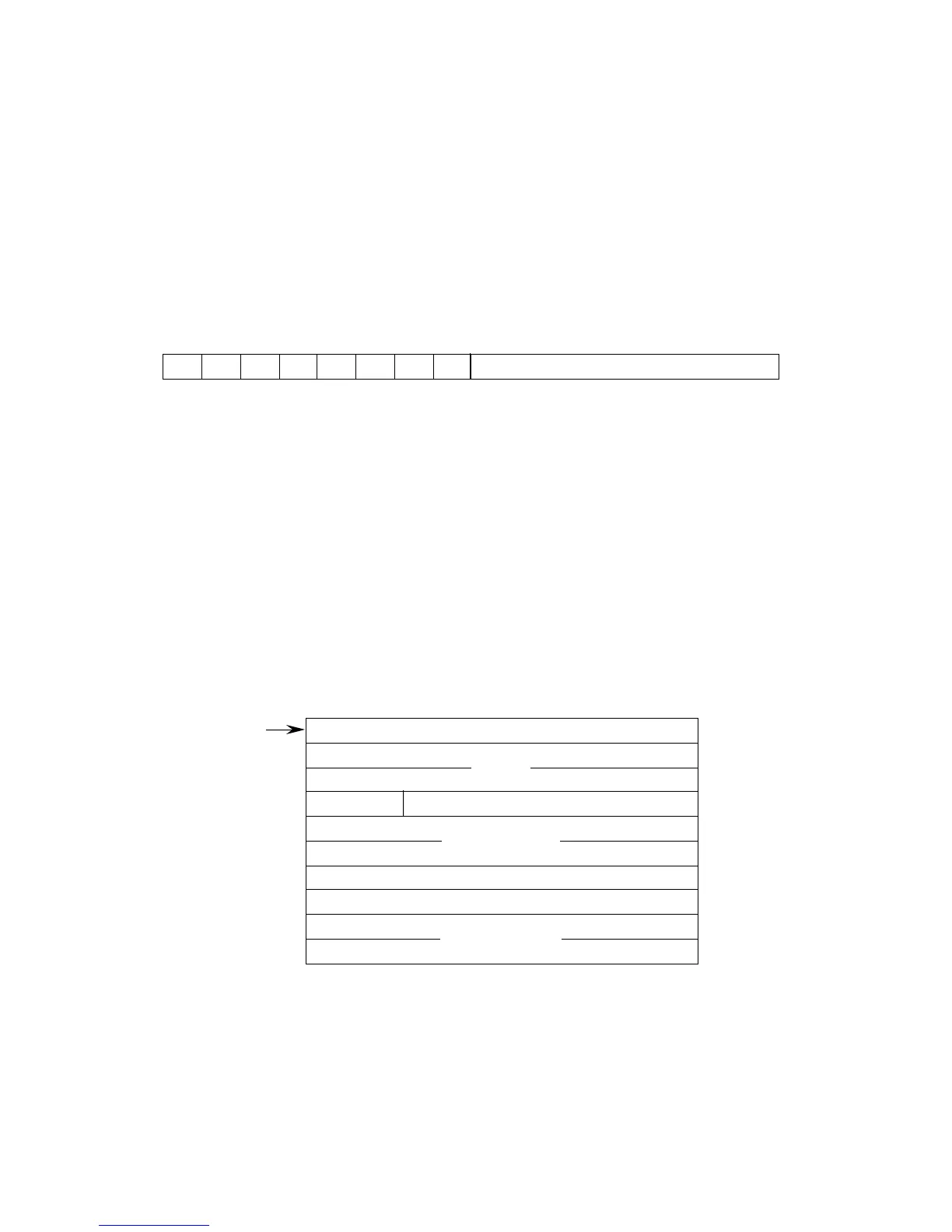

Figure 7-42 shows the format of the take midinstruction exception primitive.

15

ECTOR NUMBE

Figure 7-42. Take Midinstruction Exception Primitive Format

The take midinstruction exception primitive uses the PC bit as described in 7.4.2

Coprocessor Response Primitive General Format. The vector number field contains

the exception vector number used by the main processor to initiate exception processing.

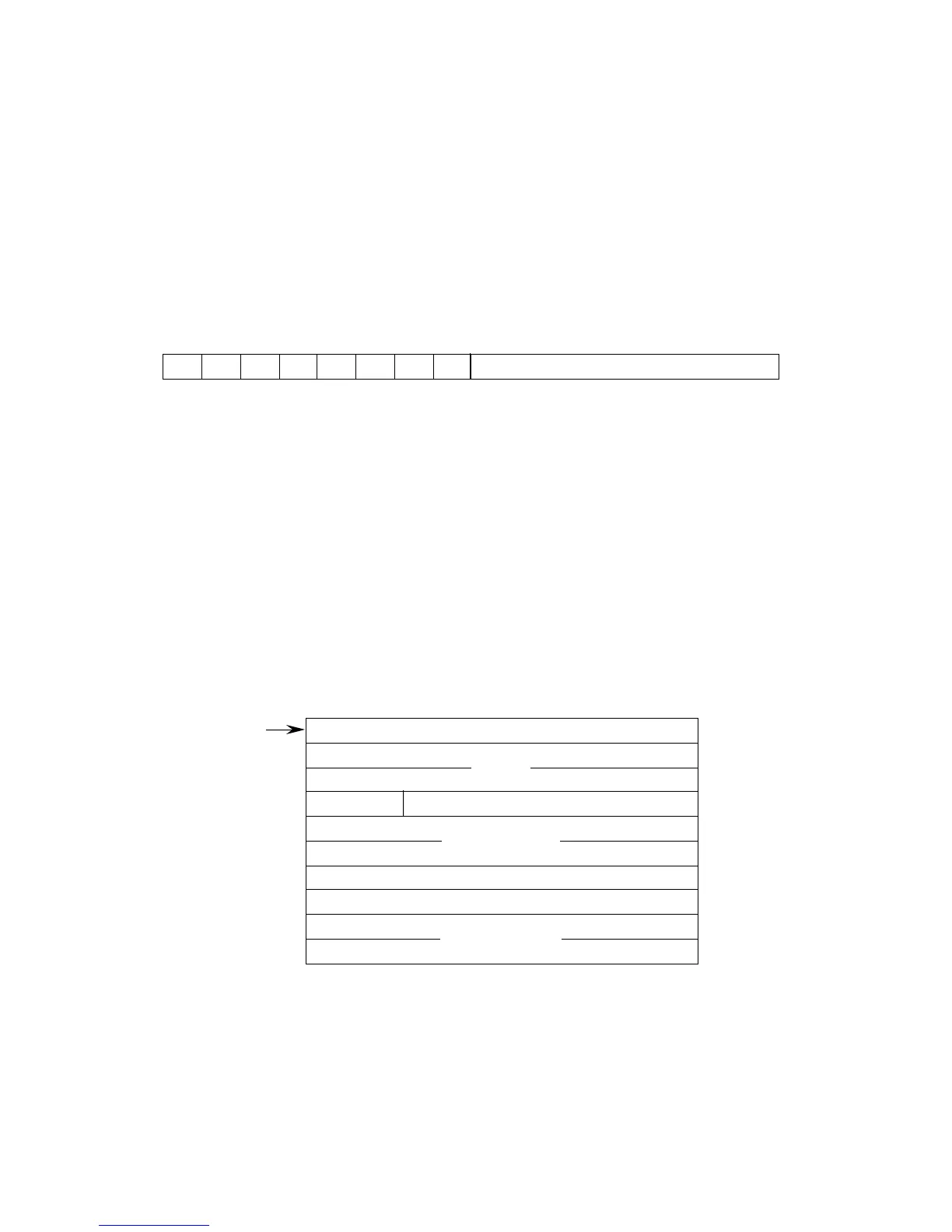

When the main processor receives this primitive, it acknowledges the coprocessor

exception request by writing an exception acknowledge mask (refer to 7.3.2 Control CIR)

to the control CIR. The MC68020/EC020 then performs exception processing as

described in Section 6 Exception Processing. The vector number for the exception is

taken from the vector number field of the primitive, and the MC68020/EC020 uses the

10-word stack frame format shown in Figure 7-43.

0

TATUS REGISTE

ECTOR NUMBE

SCAN PC

+0

+0

PROGRAM COUNTER

+0

PERATION WOR

EFFECTIVE ADDRESS

+1

NTERNAL REGISTE

+0

0

Figure 7-43. MC68020/EC020 Midinstruction Stack Frame

Loading...

Loading...