5- 20 M68020 USER’S MANUAL MOTOROLA

1 1 0 0

LONG-WORD OPERAND (REGISTER)

Figure 5-17. Misaligned Long-Word Operand Read

from Long-Word Port Example

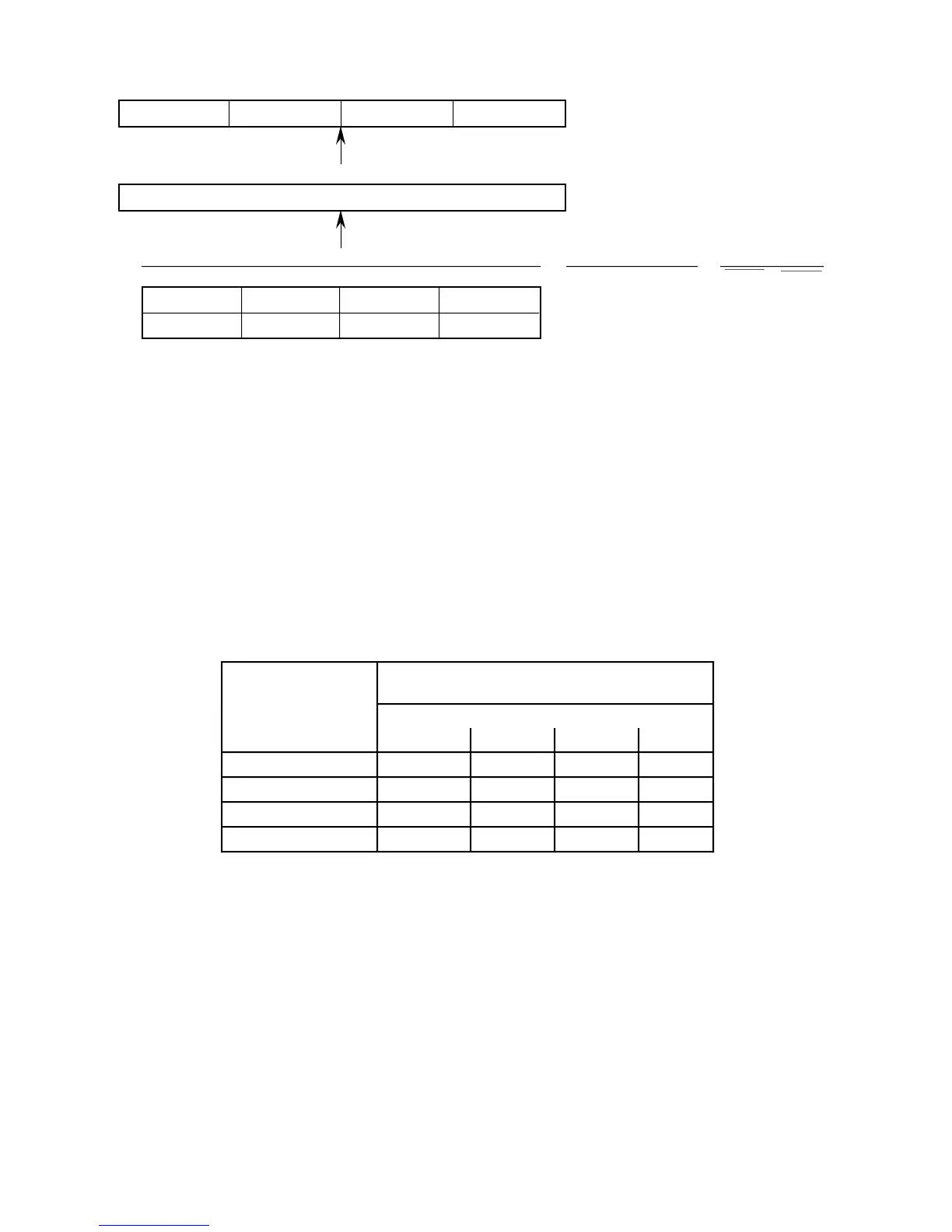

5.2.3 Effects of Dynamic Bus Sizing and Operand Misalignment

The combination of operand size, operand alignment, and port size determine the number

of bus cycles required to perform a particular memory access. Table 5-6 lists the number

of bus cycles required for different operand sizes to different port sizes with all possible

alignment conditions for read/write cycles.

Table 5-6. Memory Alignment and Port Size

Influence on Read/Write Bus Cycles

Number of Bus Cycles

(Data Port Size = 32 Bits:16 Bits:8 Bits)

A1, A0

Operand Size 00 01 10 11

Instruction* 1:2:4 N/A N/A N/A

Byte Operand 1:1:1 1:1:1 1:1:1 1:1:1

Word Operand 1:1:2 1:2:2 1:1:2 2:2:2

Long-Word Operand 1:2:4 2:3:4 2:2:4 2:3:4

*Instruction prefetches are always two words from a long-word boundary

Table 5-6 reveals that bus cycle throughput is significantly affected by port size and

alignment. The MC68020/EC020 system designer and programmer should be aware of

and account for these effects, particularly in time-critical applications.

Loading...

Loading...