5- 10 M68020 USER’S MANUAL MOTOROLA

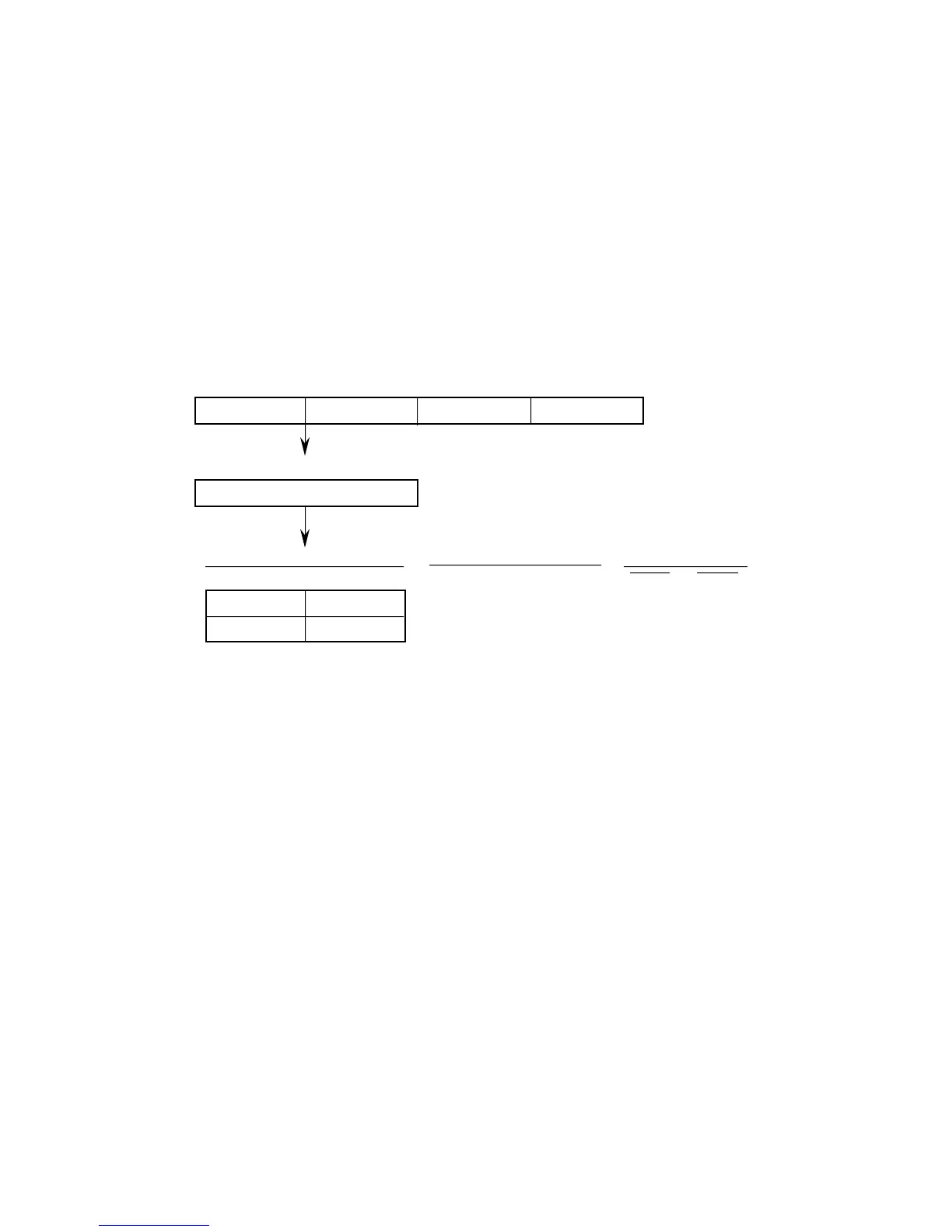

Figure 5-5 shows the transfer (write) of a long-word operand to a word port. In the first bus

cycle, the MC68020/EC020 places the four operand bytes on the external bus. Since the

address is long-word aligned in this example, the multiplexer follows the pattern in the

entry of Table 5-5 corresponding to SIZ0, SIZ1, A0, A1 = 0000. The port latches the data

on D31–D16, asserts DSACK1 (DSACK0 remains negated), and the processor terminates

the bus cycle. It then starts a new bus cycle with SIZ1, SIZ0, A1, A0 = 1010 to transfer the

remaining 16 bits. SIZ1 and SIZ0 indicate that a word remains to be transferred; A1 and

A0 indicate that the word corresponds to an offset of two from the base address. The

multiplexer follows the pattern corresponding to this configuration of SIZ1, SIZ0, A1, and

A0 and places the two least significant bytes of the long word on the word portion of the

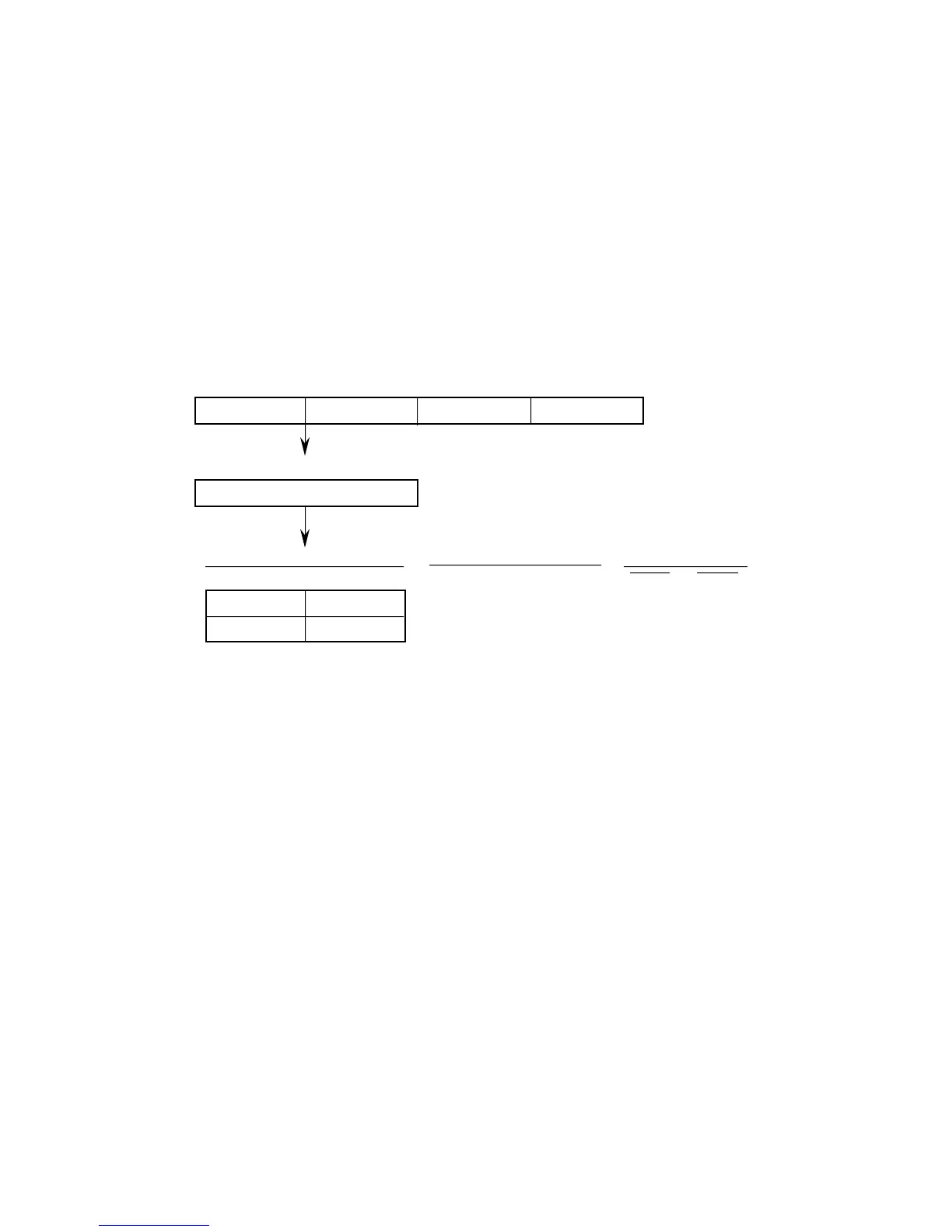

bus (D31–D16). The bus cycle transfers the remaining bytes to the word-sized port. Figure

5-6 shows the timing of the bus transfer signals for this operation.

Figure 5-5. Long-Word Operand Write to Word Port Example

Loading...

Loading...