MOTOROLA M68020 USER’S MANUAL 6- 5

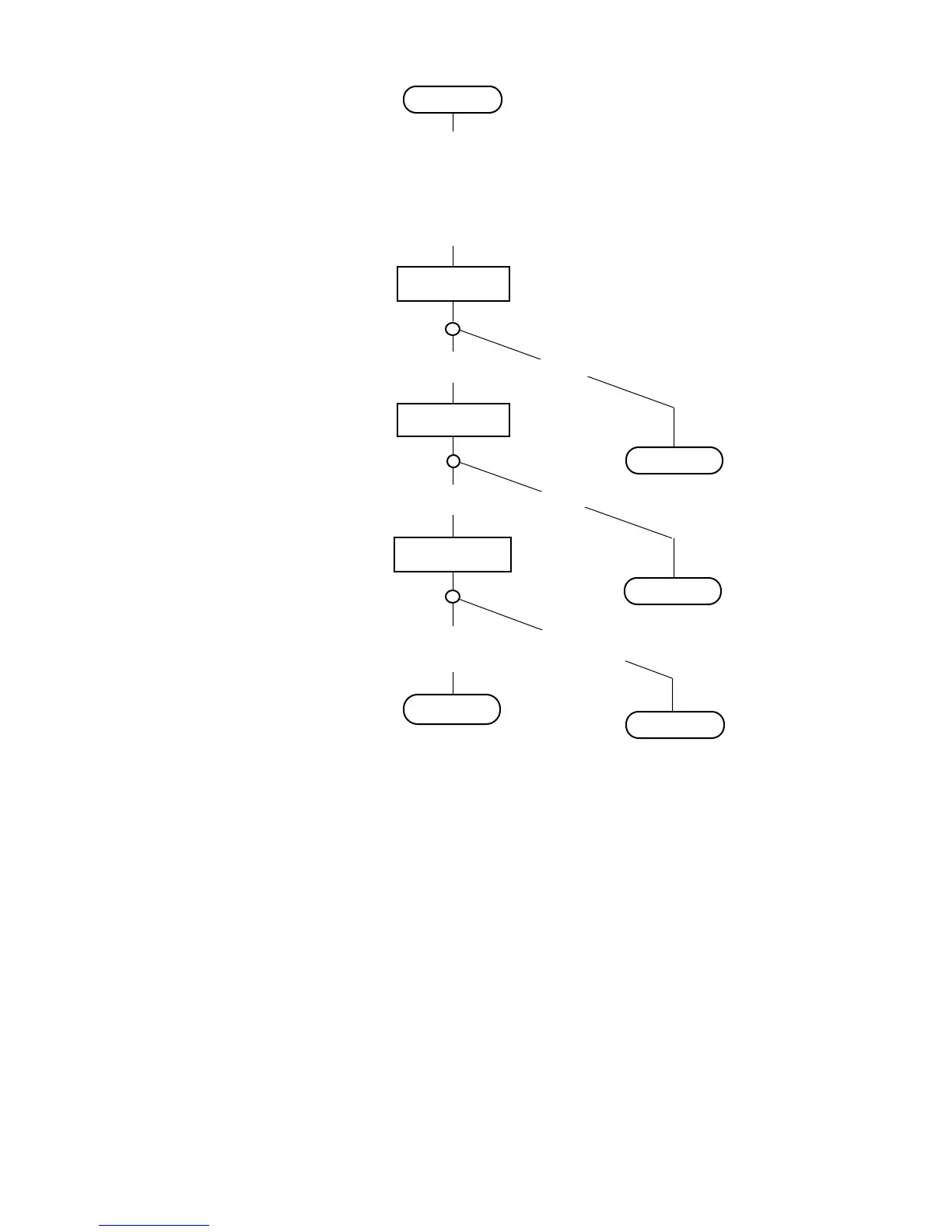

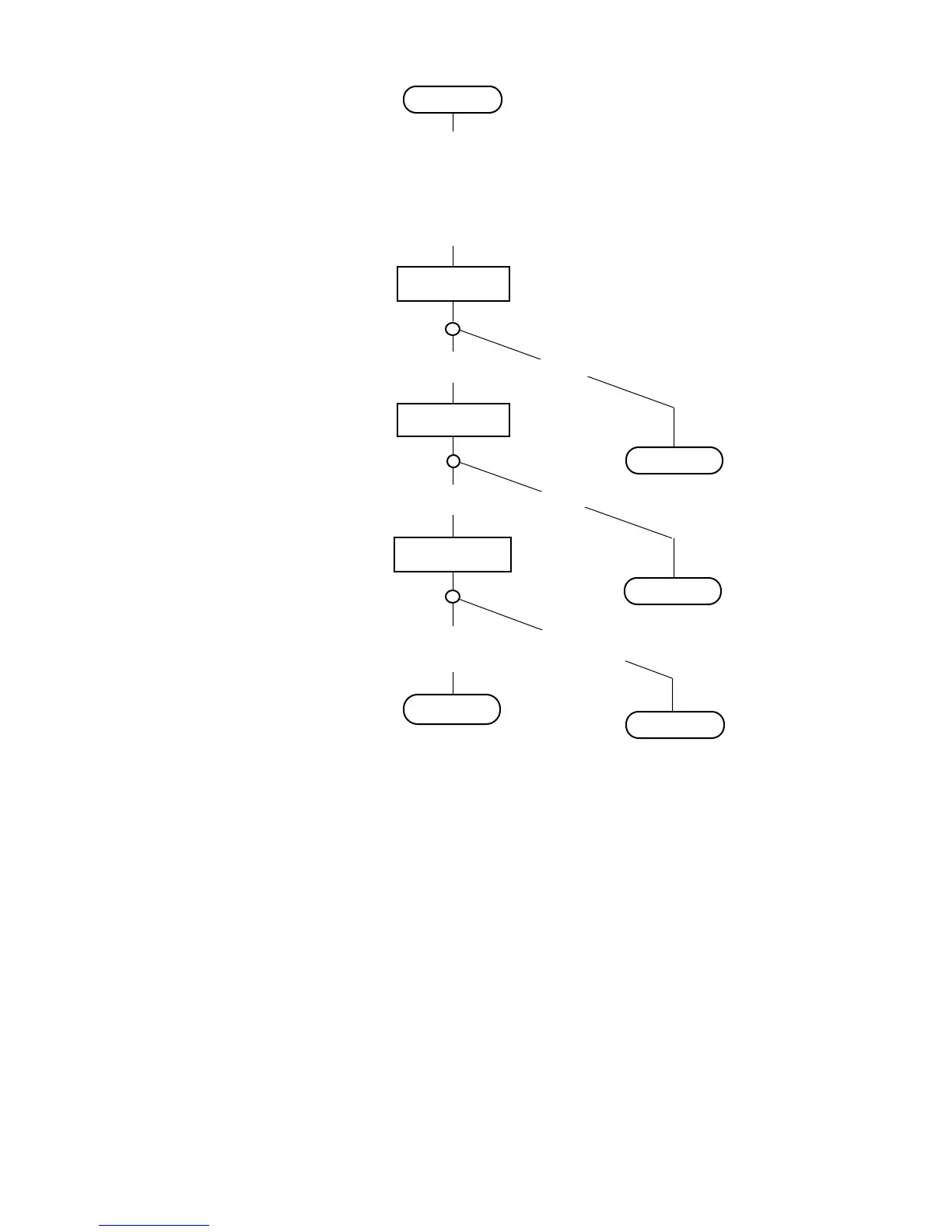

SP (VECTOR #0)

M (SR

T1, T0 (SR

I2–I0 (SR

VB

CAC

7

00000000

00000000

➧

➧

➧

➧

➧

➧

BEGIN INSTRUCTION

EXECUTION

NTRIES INVALIDATE

➧

➧

ADDRESS ERROR

Figure 6-1. Reset Operation Flowchart

The processor begins exception processing for a bus error by making an internal copy of

the current SR. The processor then enters the supervisor privilege level (by setting the S-

bit in the SR) and clears the T1 and T0 bits in the SR. The processor generates exception

vector number 2 for the bus error vector. It saves the vector offset, PC, and the internal

copy of the SR on the active supervisor stack. The saved PC value is the logical address

of the instruction that was executing at the time the fault was detected. This is not

necessarily the instruction that initiated the bus cycle since the processor overlaps

Loading...

Loading...