MOTOROLA M68020 USER’S MANUAL 7- 45

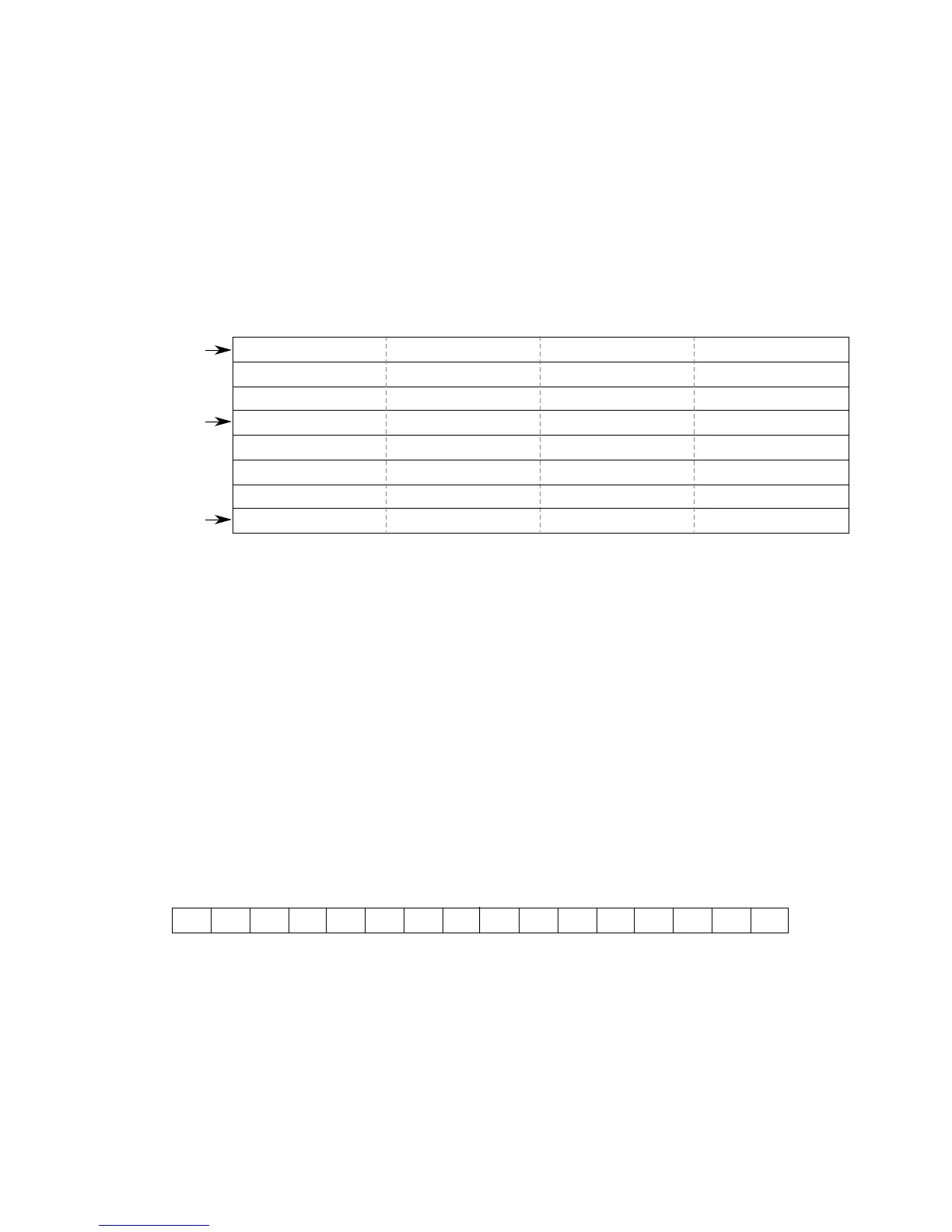

For the predecrement addressing mode, the operands are written to memory with

descending addresses, but the bytes within each operand are written to memory with

ascending addresses. As an example, Figure 7-38 shows the format in long-word-

oriented memory for two 12-byte operands transferred from the coprocessor to the

effective address using the –(An) addressing mode. The processor decrements the

address register by the size of an operand before the operand is transferred. It writes the

bytes of the operand to ascending memory addresses. When the transfer is complete, the

address register has been decremented by the total number of bytes transferred. The

MC68020/EC020 transfers the data using long-word transfers whenever possible.

P1, BYTE (0

P0, BYTE (0

P1, BYTE (L – 1

P0, BYTE (L – 1

n – LENGT

INITIAL A

OP0, Byte (0) is the first byte written to memory

OP0, Byte (L–1) is the last byte of the first operand written to memory

OP1, Byte (0) is the first byte of the second operand written to memory

OP1, Byte (L–1) is the last byte written to memory

NOTE:

An – 2 LENGT

= FINAL A

*

Figure 7-38. Operand Format in Memory for Transfer to –(An)

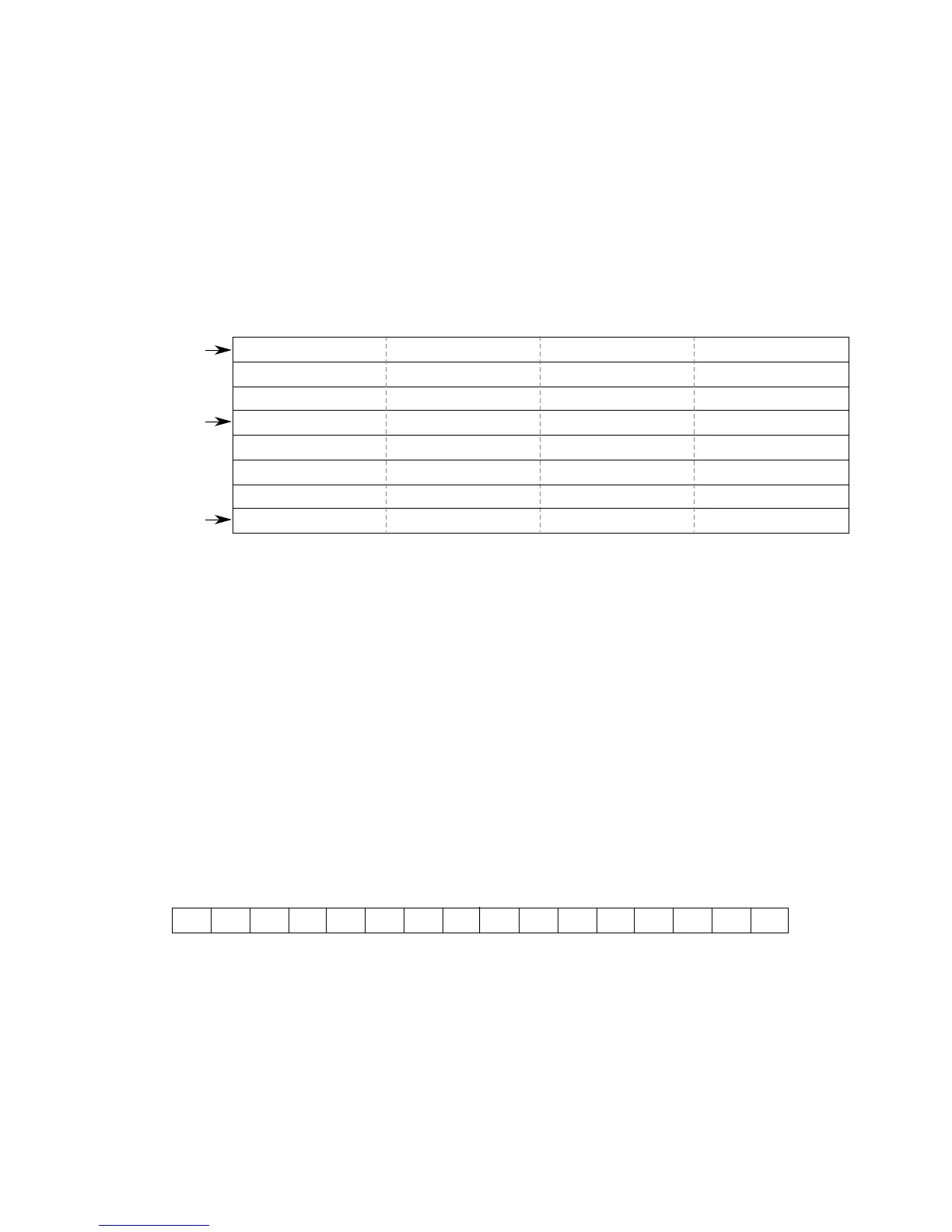

7.4.17 Transfer Status Register and ScanPC Primitive

The transfer status register and the scanPC primitive transfers values between the

coprocessor and the MC68020/EC020 SR. On an optional basis, the scanPC also makes

transfers. This primitive applies to general category instructions. If the coprocessor issues

this primitive during the execution of a conditional category instruction, the main processor

initiates protocol violation exception processing. Figure 7-39 shows the format of the

transfer status register and scanPC primitive.

15

Figure 7-39. Transfer Status Register and ScanPC Primitive Format

The transfer status register and scanPC primitive uses the CA, PC, and DR bits as

described in 7.4.2 Coprocessor Response Primitive General Format.

The SP bit selects the scanPC option. If SP = 1, the primitive transfers both the scanPC

and SR. If SP = 0, only the SR is transferred.

Loading...

Loading...