9- 4 M68020 USER’S MANUAL MOTOROLA

PAL16L8

FPCP CS GENERATION CIRCUITRY FOR 25 MHz OPERATION

MOTOROLA INC., AUSTIN, TEXAS

INPUTS: CLK ~AS FC2 FC1 FC0 A19 A18 A17 A16 A15 A14 A13

OUTPUTS: ~CS CLKD

!~CS = FC2 *FC1 *FC0 ;cpu space = $7

*!A19 *!A18 *A17 *!A16 ;coprocessor access = $2

*!A15 *!A14 *A13 ;coprocessor id = $1

*!CLK ;qualified by MPU clock low

+FC2 *FC1 *FC0 ;cpu space = $7

*!A19 *!A18 *A17 *!A16 ;coprocessor access = $2

*!A15 *!A14 *A13 ;coprocessor id = $1

*!~AS ;qualified by address strobe low

+FC2 *FC1 *FC0 ;cpu space = $7

*!A19 *!A18 *A17 *!A16 ;coprocessor access = $2

*!A15 *!A14 *A13 ;coprocessor id = $1

*CLKD ;qualified by CLKD (delayed CLK)

CLKD = CLK

Description: There are three terms to the CS generation. The first term denotes the earliest time CS can be asserted.

The second term is used to assert

CS until the end of the FPCP access. The third term is to ensure that no race

condition occurs in case of a late

AS.

Figure 9-3. Chip Select PAL Equations

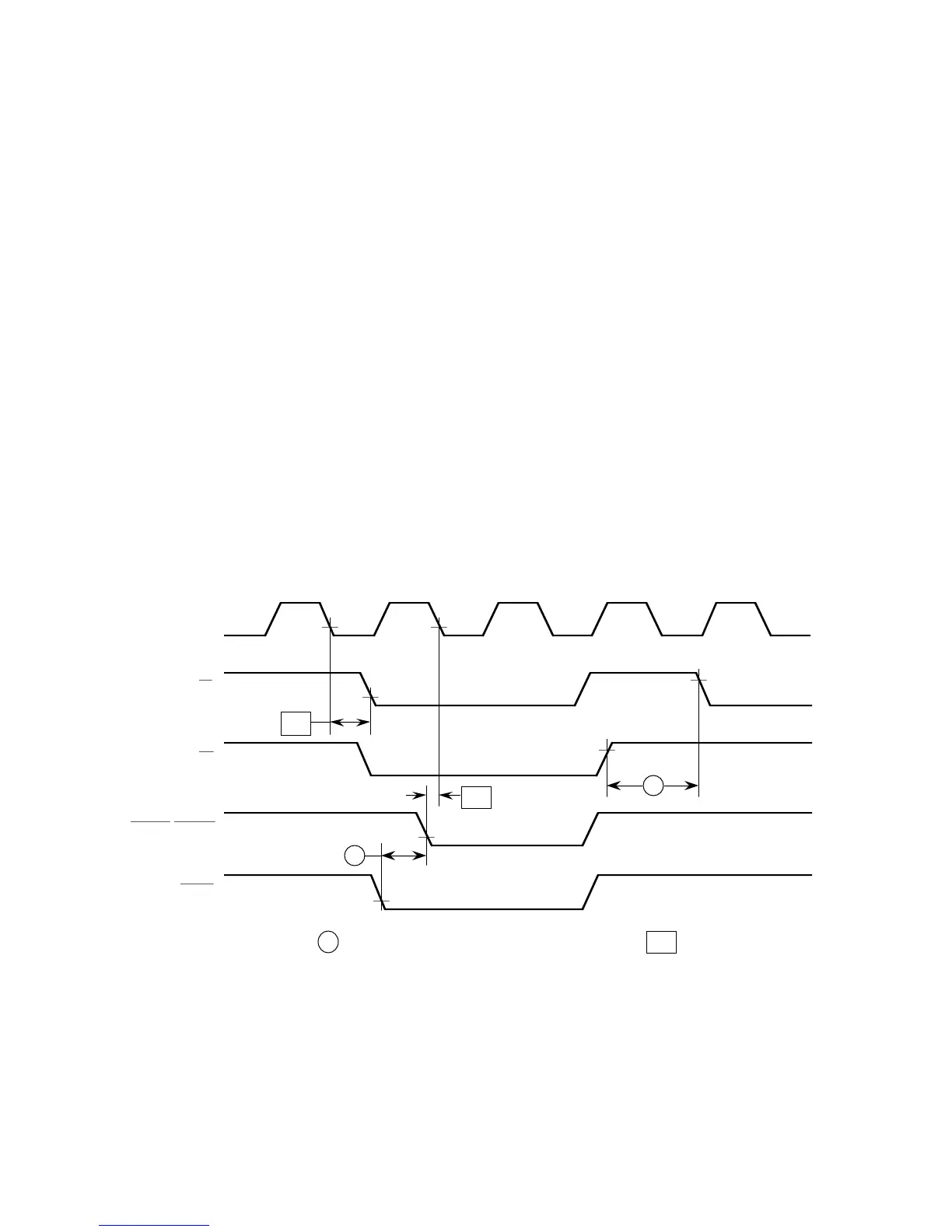

Figure 9-4. Bus Cycle Timing Diagram

Loading...

Loading...