8- 6 M68020 USER’S MANUAL MOTOROLA

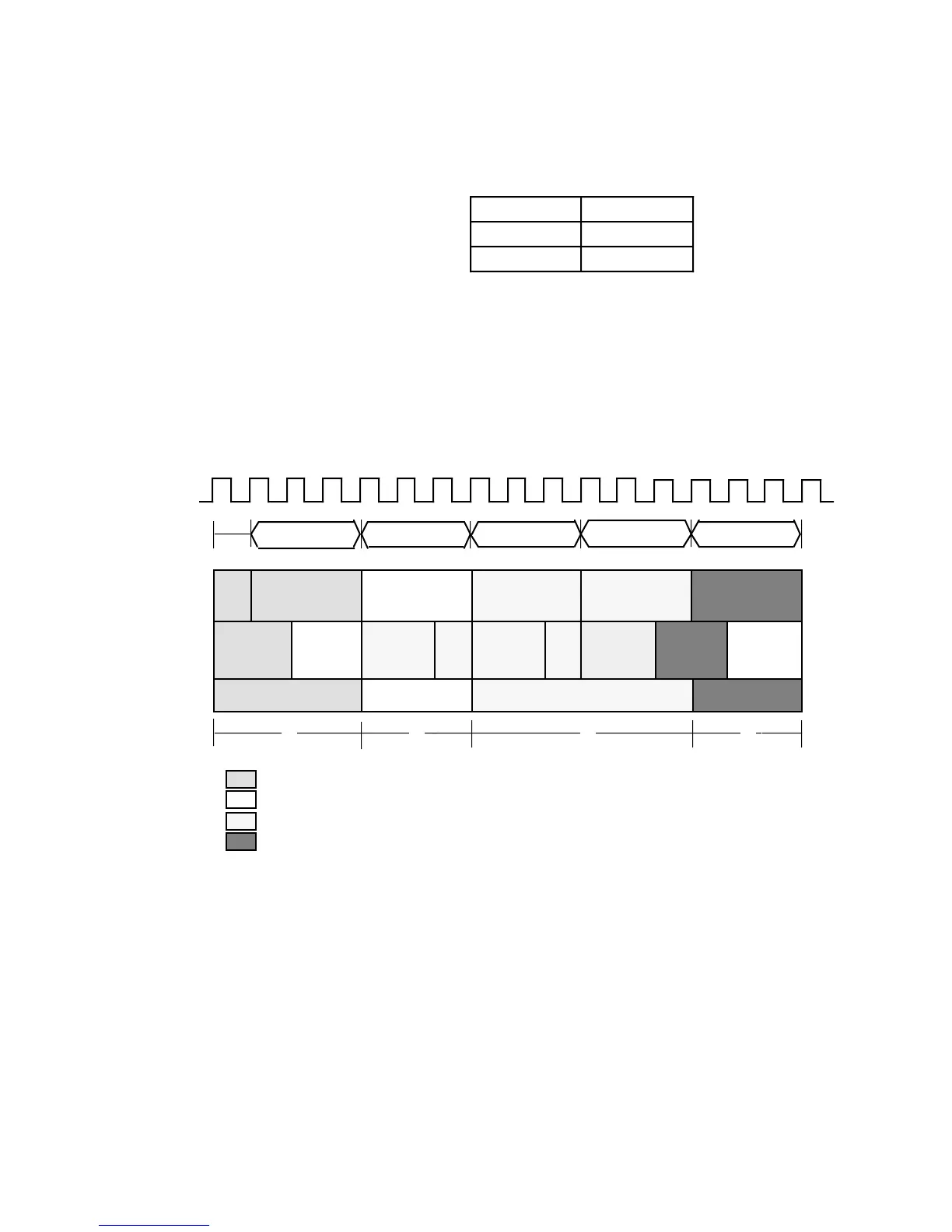

Example 2

Using the same instruction stream, the second example demonstrates the different effects

of instruction execution overlap on instruction timing when the same instructions are

positioned slightly differently in 32-bit memory:

Address n MOVE #1 ADD #2

n + 4 MOVE #3 ADD #4

n + 8 ••• •••

The assumptions for example 2 (see Figure 8-4) are:

1. The data bus is 32 bits,

2. The first instruction is prefetched from an even-word address,

3. Memory access occurs with no wait states, and

4. The cache is disabled.

ACTIVIT

BYTES n + 1

ONTROLLE

BYTES n + 8

MOVE #1

ADD #2

OURCE E

MOVE #3

ESTINATIO

EA

MOVE #3

MOVE #3

XECUTION TIM

COUNTE

NSTRUCTIO

ADD #4

Figure 8-4. Processor Activity for Example 2

Although the total execution time of the instruction segment does not change in this

example, the individual instruction times are significantly different. This example

demonstrates that the effects of overlap are not only instruction-sequence dependent but

are also dependent upon the alignment of the instruction stream in memory.

Loading...

Loading...