6- 12 M68020 USER’S MANUAL MOTOROLA

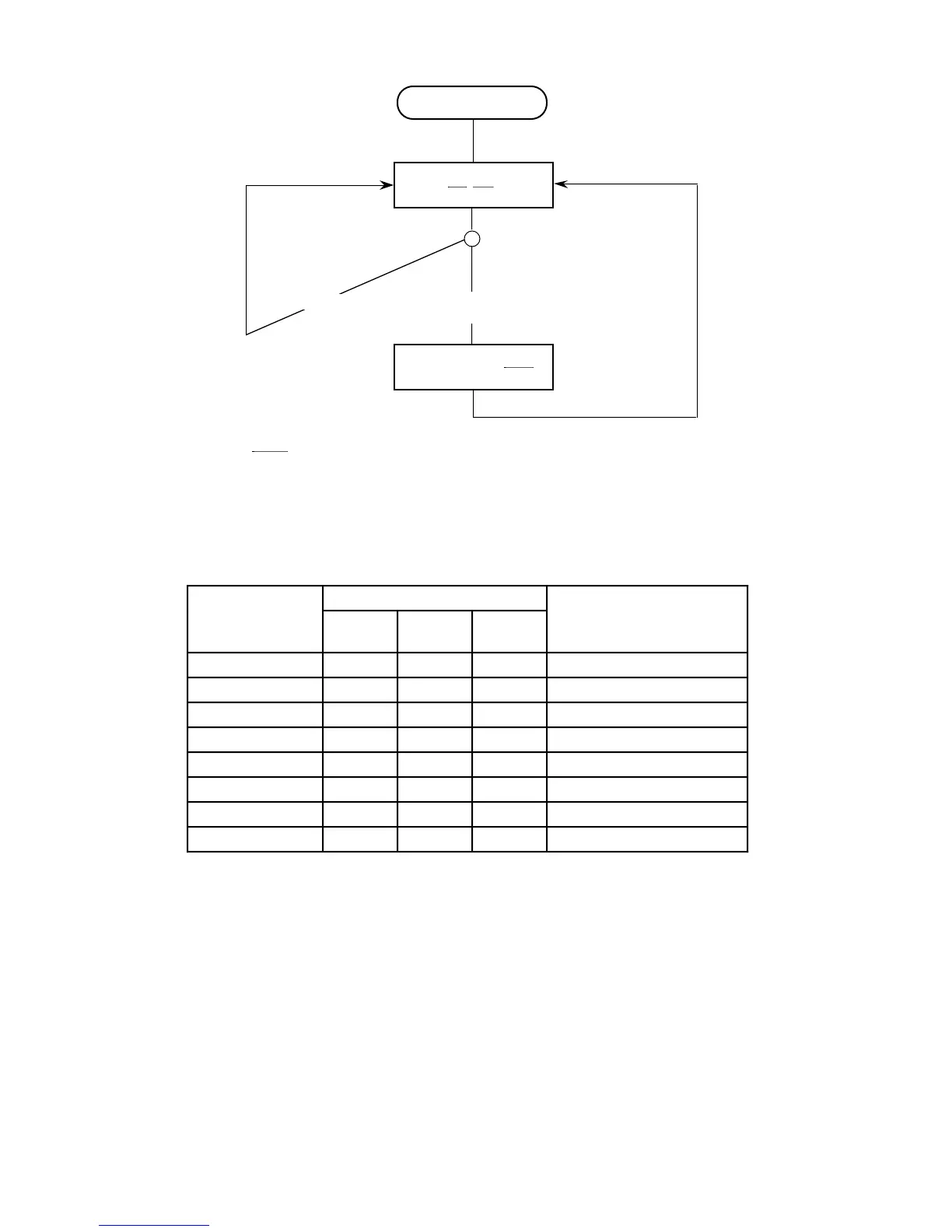

IPL2–IPL0

(MC68020 ASSERTS IPEND

(COMPARE INTERRUPT LEVEL

W

ITH STATUS REGISTER MASK

OR TRANSITION ON LEVEL 7

>

IPEND is not implemented in the MC68EC020.

Figure 6-2. Interrupt Pending Procedure

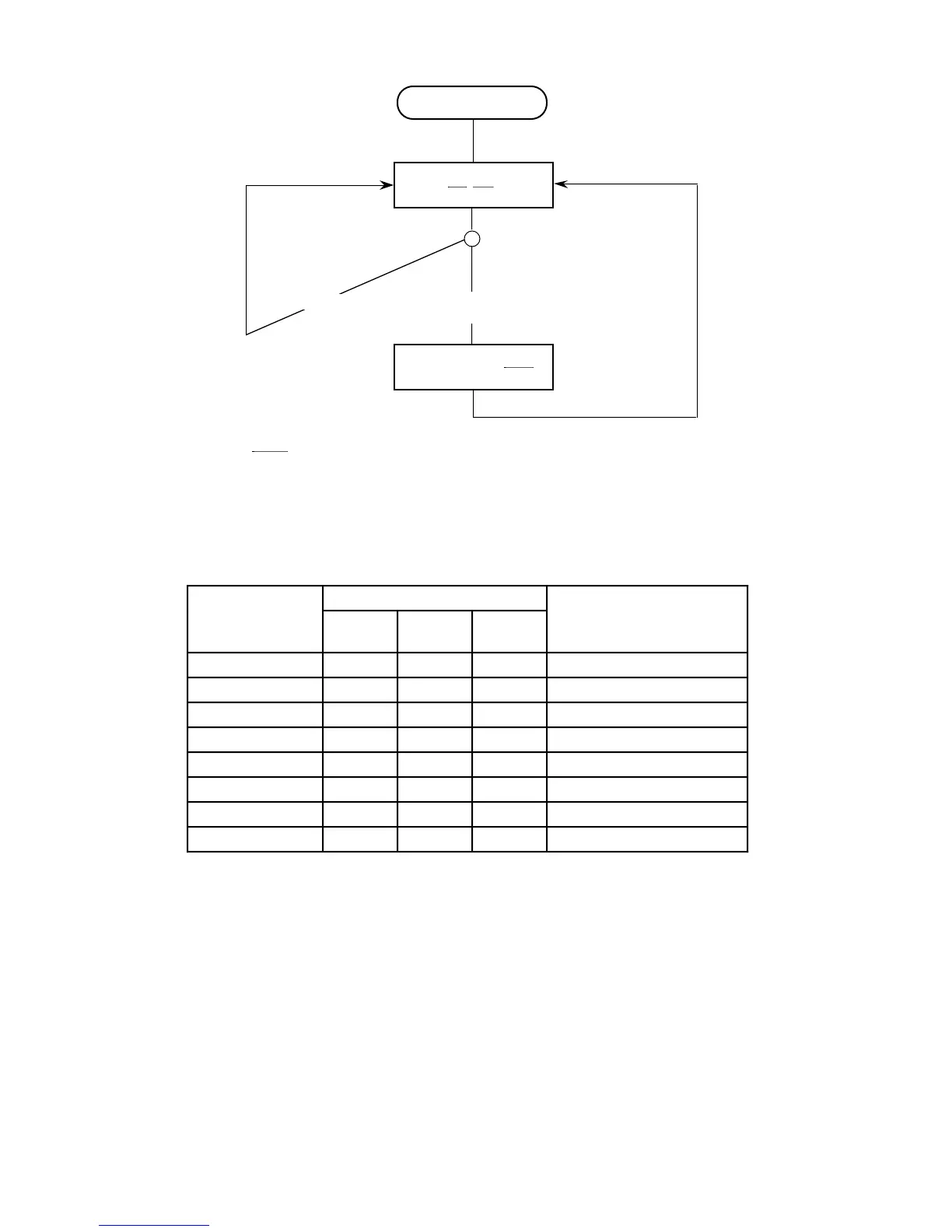

Table 6-3. Interrupt Levels and Mask Values

Control Line Status

Requested

Interrupt Level

IPL2 IPL1 IPL0

Interrupt Mask Value

Required for Recognition

0* NNN N/A*

1 NNA 0

2 N A N 1–0

3 N A A 2–0

4 A N N 3–0

5 A N A 4–0

6 AAN 5–0

7 AAA 7–0

*Indicates that no interrupt is requested.

A—Asserted

N—Negated

Priority level 7, the nonmaskable interrupt, is a special case. Level 7 interrupts cannot be

masked by the interrupt priority mask, and they are transition sensitive. The processor

recognizes an interrupt request each time the external interrupt request level changes

from some lower level to level 7, regardless of the value in the mask. Figure 6-3 shows

two examples of interrupt recognitions, one for level 6 and one for level 7. When the

MC68020/EC020 processes a level 6 interrupt, the interrupt priority mask is automatically

updated with a value of 6 before entering the handler routine so that subsequent level 6

interrupts are masked. Provided no instruction that lowers the mask value is executed, the

Loading...

Loading...