MOTOROLA M68020 USER’S MANUAL 8- 7

Example 3

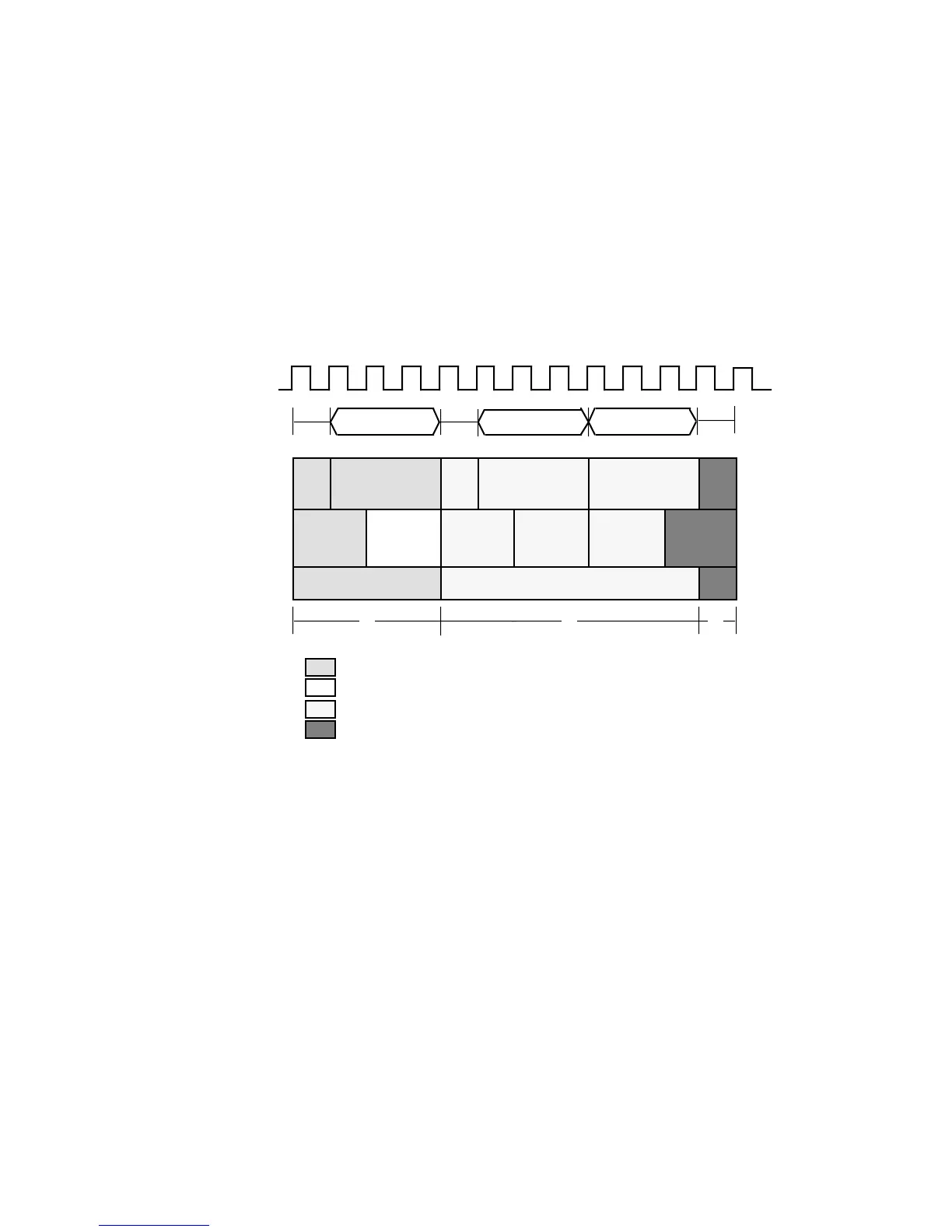

Both Figures 8-3 and 8-4 show instruction execution without benefit of the

MC68020/EC020 instruction cache. Figure 8-5 shows a third example for the same

instruction stream executing in the cache. Note that once the instructions are in the cache,

the original location in external memory is no longer a factor in timing.

The assumptions for Example 3 are:

1. The data bus is 32 bits,

2. The cache is enabled and instructions are in the cache, and

3. Memory access occurs with no wait states.

ACTIVIT

ONTROLLE

MOVE #1

ADD #2

OURCE E

MOVE #3

ESTINATIO

EA

MOVE #3

MOVE #3

D5,D

XECUTION TIM

COUNTE

ADD #4

Figure 8-5. Processor Activity for Example 3

Figure 8-5 illustrates the benefits of the instruction cache. The total number of clock cycles

is reduced from 16 to 12 clocks. Since the instructions are resident in the cache, the

instruction prefetch activity does not require the bus controller to perform external bus

cycles. Since prefetch occurs with no delay, the bus controller is idle more often.

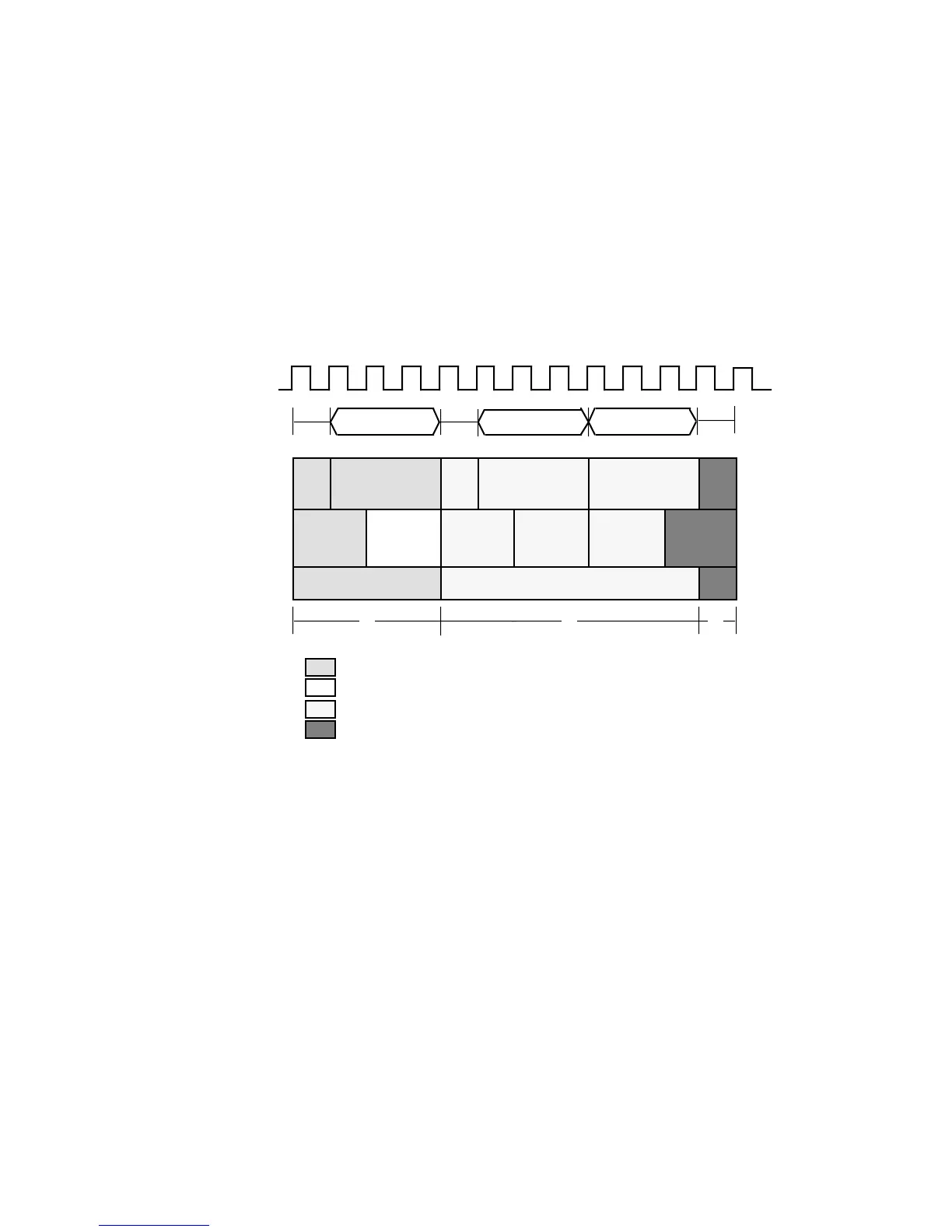

Example 4

Idle clock cycles, such as those shown in example 3, are useful in MC68020/EC020

systems that require wait states when accessing external memory. This fact is illustrated

in example 4 (see Figure 8-6) with the following assumptions:

1. The data bus is 32 bits,

2. The cache is enabled and instructions are in the cache, and

3. Memory access occurs with one wait state.

Loading...

Loading...