MOTOROLA M68020 USER’S MANUAL 8- 33

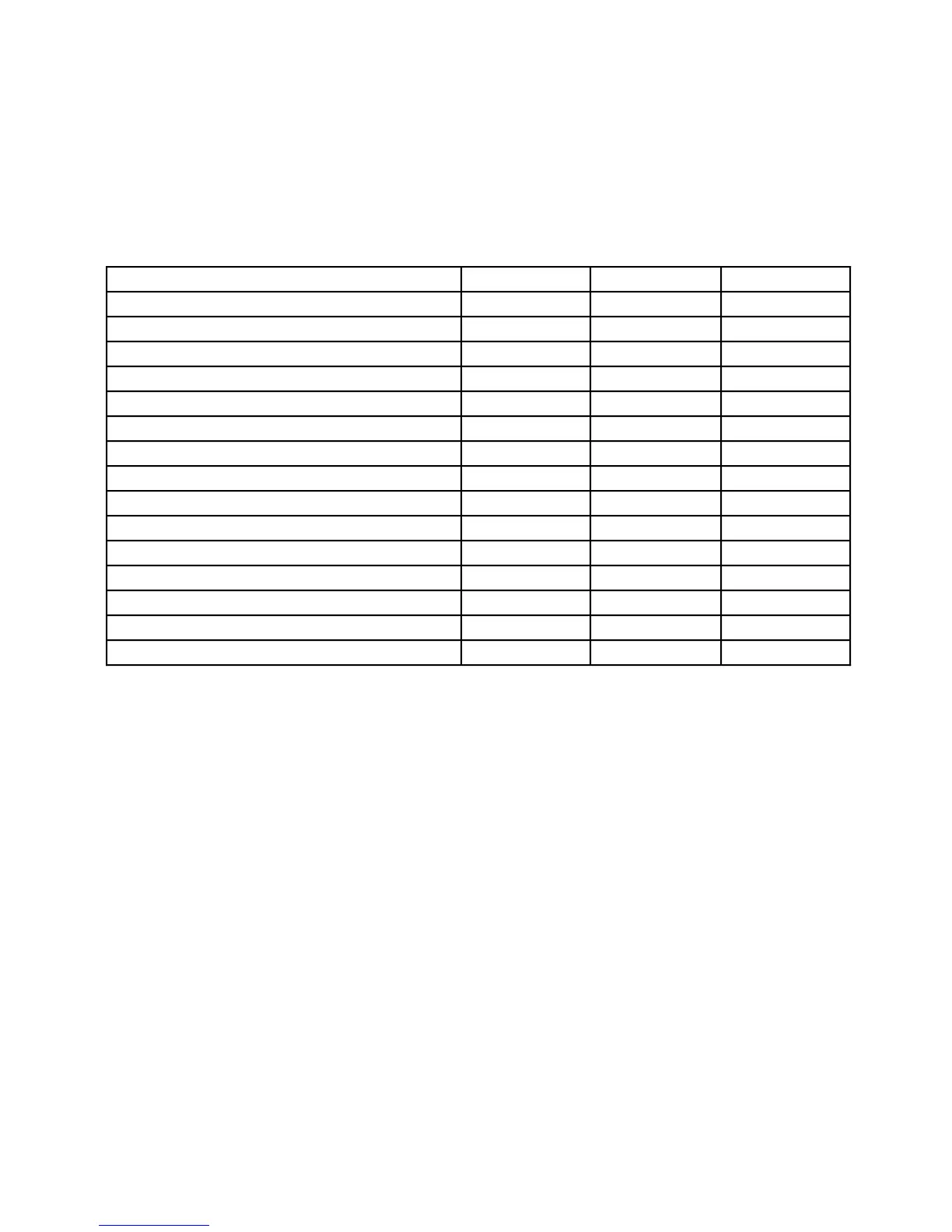

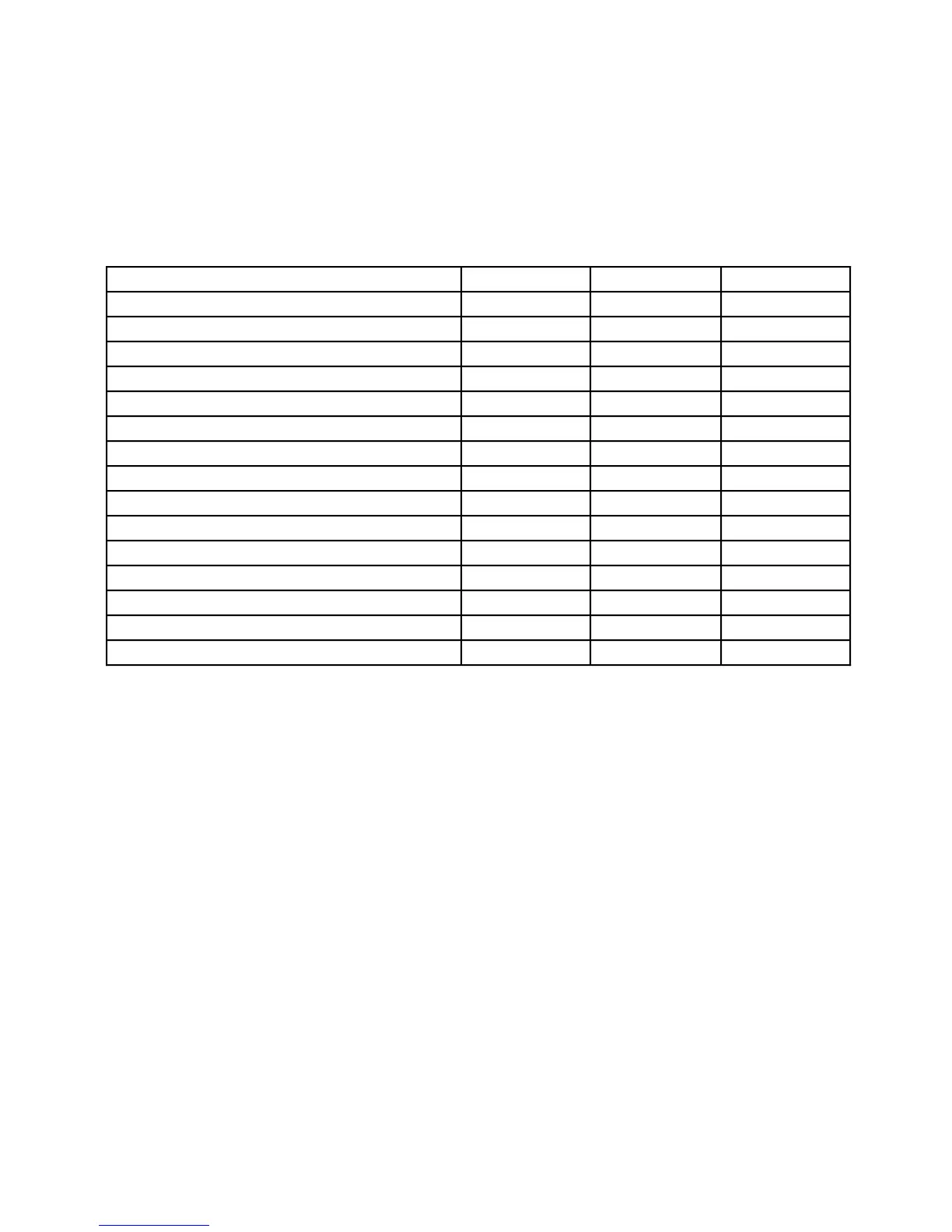

8.2.11 Single-Operand Instructions

The single-operand instructions table indicates the number of clock periods needed for the

processor to perform the specified operation on the given addressing mode. Footnotes

indicate when it is necessary to add another table entry to calculate the total effective

execution time for the instruction. The total number of clock cycles is outside the

parentheses; the number of read, prefetch, and write cycles is given inside the

parentheses as (r/p/w). These cycles are included in the total clock cycle number.

Instruction Best Case Cache Case Worst Case

CLR Dn 0(0/0/0) 2(0/0/0) 3(0/1/0)

† CLR Mem 3(0/0/1) 4(0/0/1) 6(0/1/1)

NEG Dn 0(0/0/0) 2(0/0/0) 3(0/1/0)

* NEG Mem 3(0/0/1) 4(0/0/1) 6(0/1/1)

NEGX Dn 0(0/0/0) 2(0/0/0) 3(0/1/0)

* NEGX Mem 3(0/0/1) 4(0/0/1) 6(0/1/1)

NOT Dn 0(0/0/0) 2(0/0/0) 3(0/1/0)

* NOT Mem 3(0/0/1) 4(0/0/1) 6(0/1/1)

EXT Dn 1(0/0/0) 4(0/0/0) 4(0/1/0)

NBCD Dn 6(0/0/0) 6(0/0/0) 6(0/1/0)

Scc Dn 1(0/0/0) 4(0/0/0) 4(0/1/0)

† Scc Mem 6(0/0/1) 6(0/0/1) 6(0/1/1)

TAS Dn 1(0/0/0) 4(0/0/0) 4(0/1/0)

† TAS Mem 12(1/0/1) 12(1/0/1) 13(1/1/1)

* TST EA 0(0/0/0) 2(0/0/0) 3(0/1/0)

*Add Fetch Effective Address Time

†Add Calculate Effective Address Time

Loading...

Loading...