RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 172

Dec 10, 2015

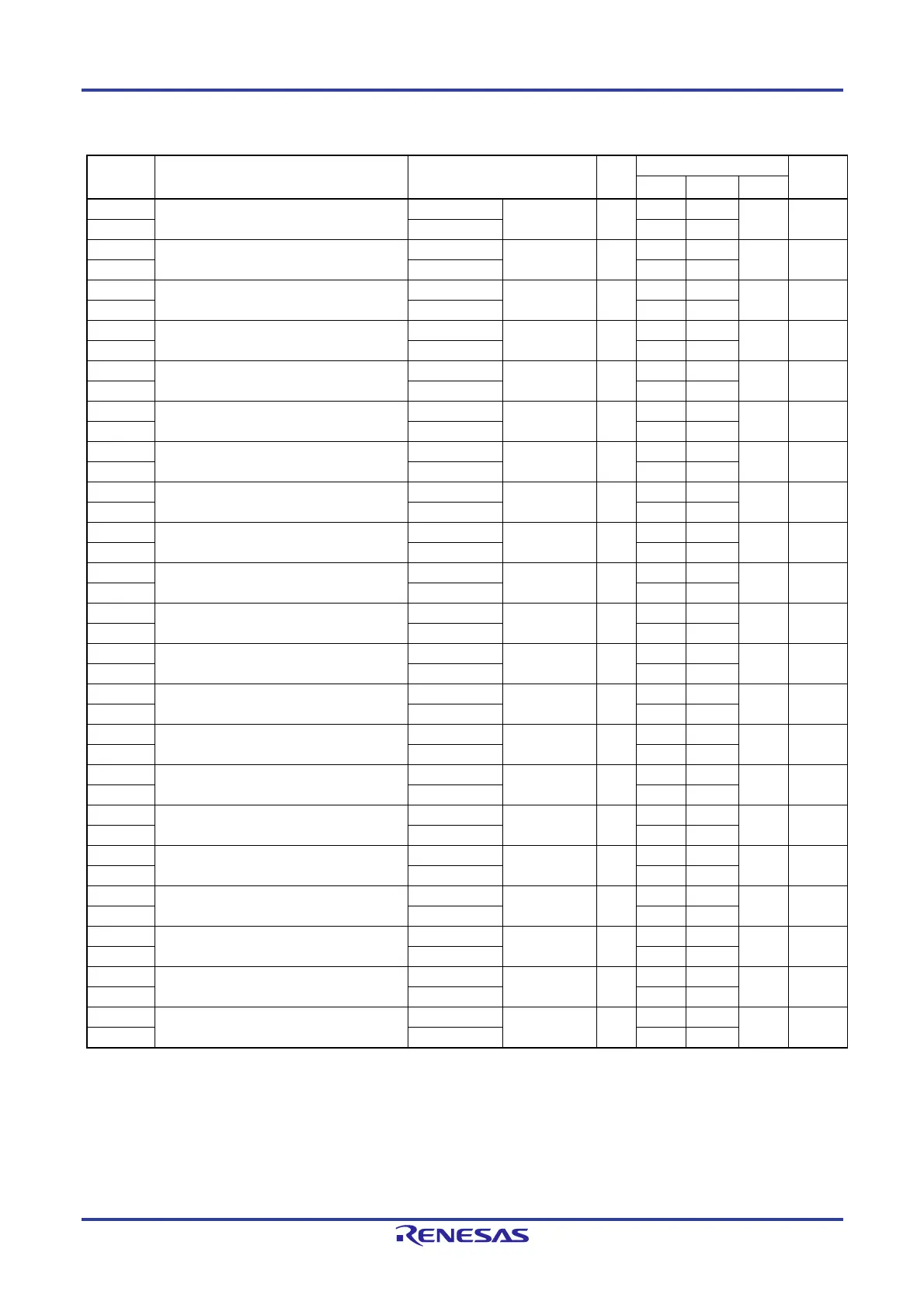

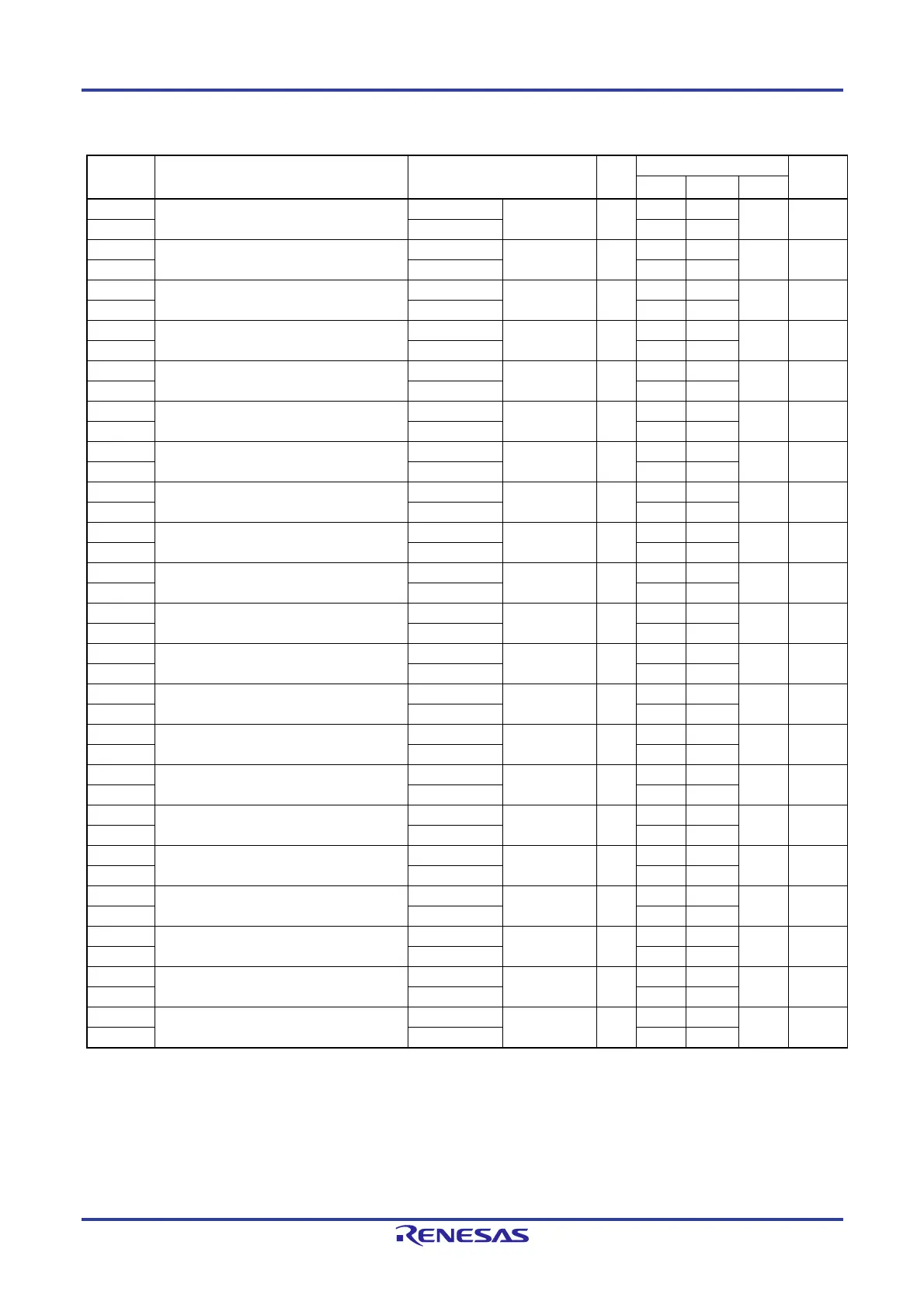

Table 3-6. Extended SFR (2nd SFR) List (21/32)

Address Special Function Register (2nd SFR) Name Symbol R/W Manipulable Bit Range After

reset

1-bit 8-bit 16-bit

F045AH CAN receive rule entry register 15BH

Note 1

GAFLMH15L GAFLMH15 R/W – √ √ 0000H

F045BH GAFLMH15H – √

F045AH CAN receive buffer register 11CH

Note 2

RMDF111L RMDF111 R – √ √ 0000H

F045BH RMDF111H – √

F045CH CAN receive rule entry register 15CL

Note 1

GAFLPL15L GAFLPL15 R/W – √ √ 0000H

F045DH GAFLPL15H – √

F045CH CAN receive buffer register 11DL

Note 2

RMDF211L RMDF211 R – √ √ 0000H

F045DH RMDF211H – √

F045EH CAN receive rule entry register 15CH

Note 1

GAFLPH15L GAFLPH15 R/W – √ √ 0000H

F045FH GAFLPH15H – √

F045EH CAN receive buffer register 11DH

Note 2

RMDF311L RMDF311 R – √ √ 0000H

F045FH RMDF311H – √

F0460H CAN receive buffer register 12AL

Note 2

RMIDL12L RMIDL12 R – √ √ 0000H

F0461H RMIDL12H – √

F0462H CAN receive buffer register 12AH

Note 2

RMIDH12L RMIDH12 R – √ √ 0000H

F0463H RMIDH12H – √

F0464H CAN receive buffer register 12BL

Note 2

RMTS12L RMTS12 R – √ √ 0000H

F0465H RMTS12H – √

F0466H CAN receive buffer register 12BH

Note 2

RMPTR12L RMPTR12 R – √ √ 0000H

F0467H RMPTR12H – √

F0468H CAN receive buffer register 12CL

Note 2

RMDF012L RMDF012 R – √ √ 0000H

F0469H RMDF012H – √

F046AH CAN receive buffer register 12CH

Note 2

RMDF112L RMDF112 R – √ √ 0000H

F046BH RMDF112H – √

F046CH CAN receive buffer register 12DL

Note 2

RMDF212L RMDF212 R – √ √ 0000H

F046DH RMDF212H – √

F046EH CAN receive buffer register 12DH

Note 2

RMDF312L RMDF312 R – √ √ 0000H

F046FH RMDF312H – √

F0470H CAN receive buffer register 13AL

Note 2

RMIDL13L RMIDL13 R – √ √ 0000H

F0471H RMIDL13H – √

F0472H CAN receive buffer register 13AH

Note 2

RMIDH13L RMIDH13 R – √ √ 0000H

F0473H RMIDH13H – √

F0474H CAN receive buffer register 13BL

Note 2

RMTS13L RMTS13 R – √ √ 0000H

F0475H RMTS13H – √

F0476H CAN receive buffer register 13BH

Note 2

RMPTR13L RMPTR13 R – √ √ 0000H

F0477H RMPTR13H – √

F0478H CAN receive buffer register 13CL

Note 2

RMDF013L RMDF013 R – √ √ 0000H

F0479H RMDF013H – √

F047AH CAN receive buffer register 13CH

Note 2

RMDF113L RMDF113 R – √ √ 0000H

F047BH RMDF113H – √

F047CH CAN receive buffer register 13DL

Note 2

RMDF213L RMDF213 R – √ √ 0000H

F047DH RMDF213H – √

Notes 1. These registers are allocated to the RAM window 0 for the CAN module (receive rule and CAN RAM test register).

When setting these registers, set the RPAGE bit in the GRWCR register to 0.

2. These registers are allocated to the RAM window 1 for the CAN module (receive buffer, receive FIFO buffer,

transmit/receive FIFO buffer, transmit buffer, and transmit history data). When setting these registers, set the

RPAGE bit in the GRWCR register to 1.

Loading...

Loading...