RL78/F13, F14 CHAPTER 27 SAFETY FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1592

Dec 10, 2015

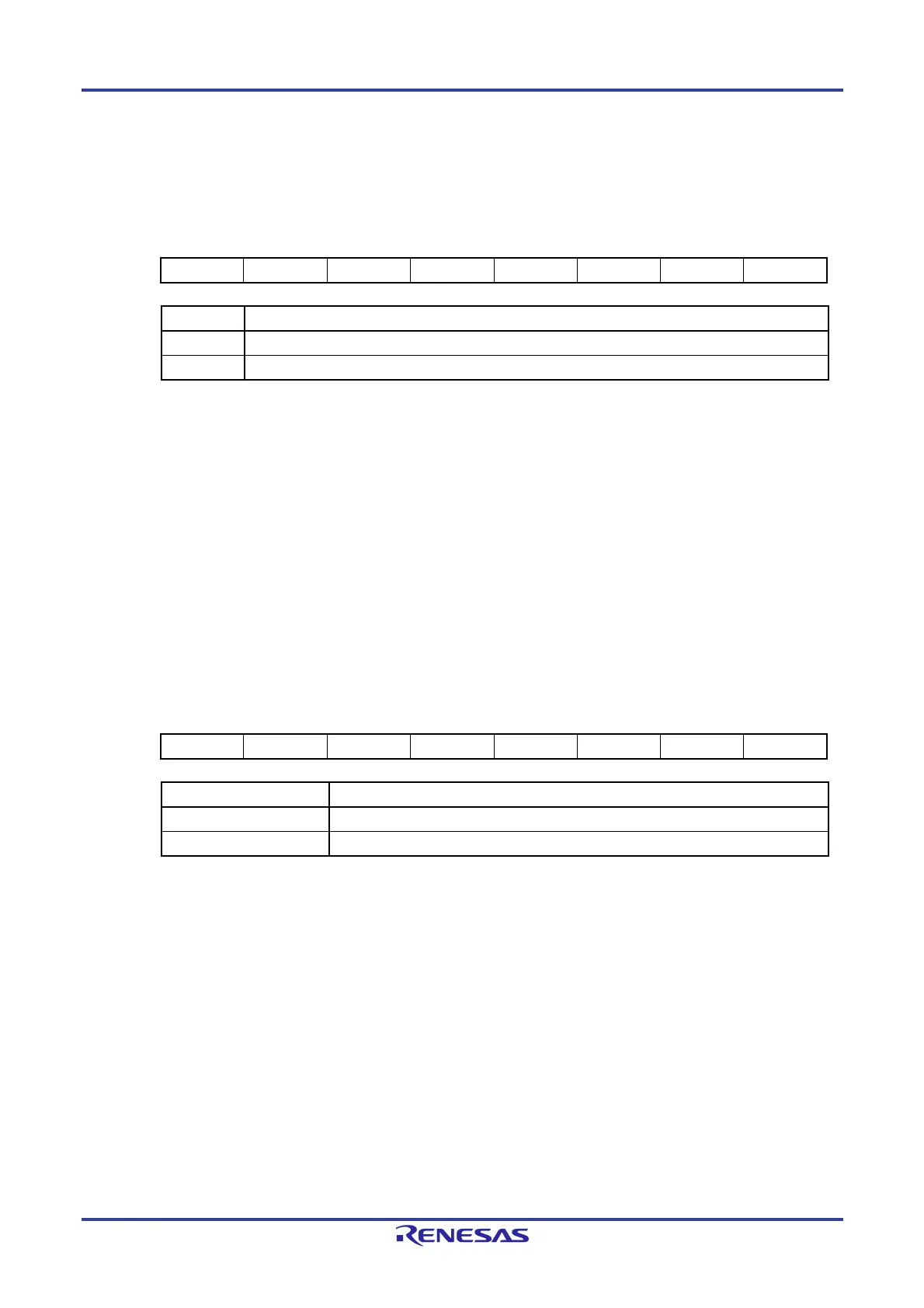

(3) Bit error detection register (ECCER)

Figure 27-10. Format of Bit Error Detection Register (ECCER)

Address: F0203H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

ECCER - - - - - - - DBERR

DBERR Bit error detection flag

0 A 1-bit error detected.

1 A 2-bit error detected.

Cautions 1. The DBERR bit is cleared to 0 by writing 0.

2. If setting to 1 due to bit error detection and clearing to 0 by the CPU occur simultaneously,

setting to 1 due to bit error detection has a priority.

3. If a bit error detection interrupt request (INTRAM) is not generated, the DBERR value is

invalid.

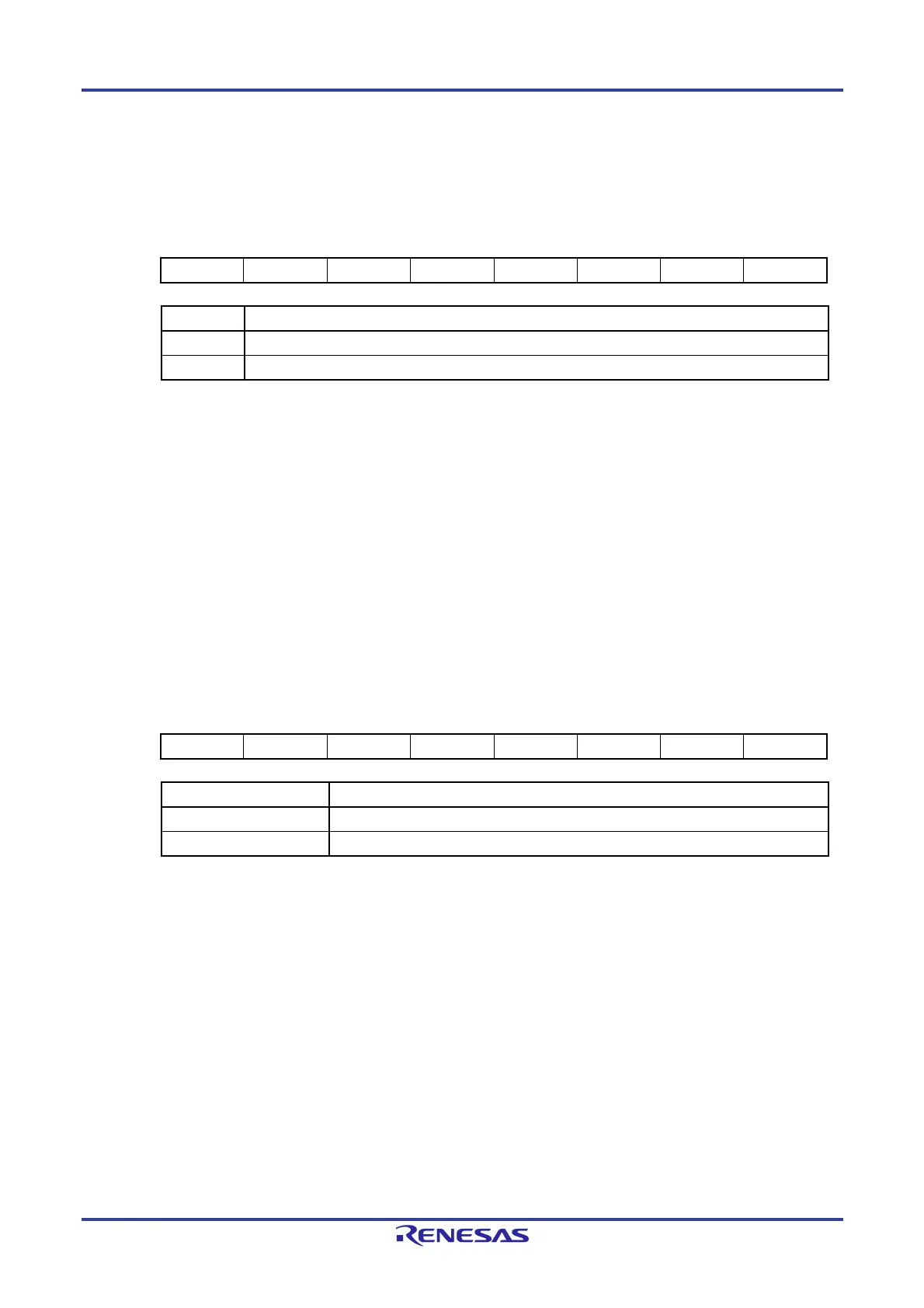

(4) ECC test protect register (ECCTPR)

This register is used to prevent accidentally changing the setting of the ECCTMDR register to trigger entry to the ECC

test mode.

Writing a value other than 07H prevents changes to the value of the ECCTMDR register

Figure 27-11. Format of ECC Test Protect Register (ECCTPR)

Address: F0204H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

ECCTPR - - - - - TPR2 TPR1 TPR0

TPR2 to TPR0 ECC test protect bits

Other than 00000111 Access to the ECCTMDR register is disabled.

00000111 Access to the ECCTMDR register is enabled.

Loading...

Loading...