RL78/F13, F14 CHAPTER 27 SAFETY FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1591

Dec 10, 2015

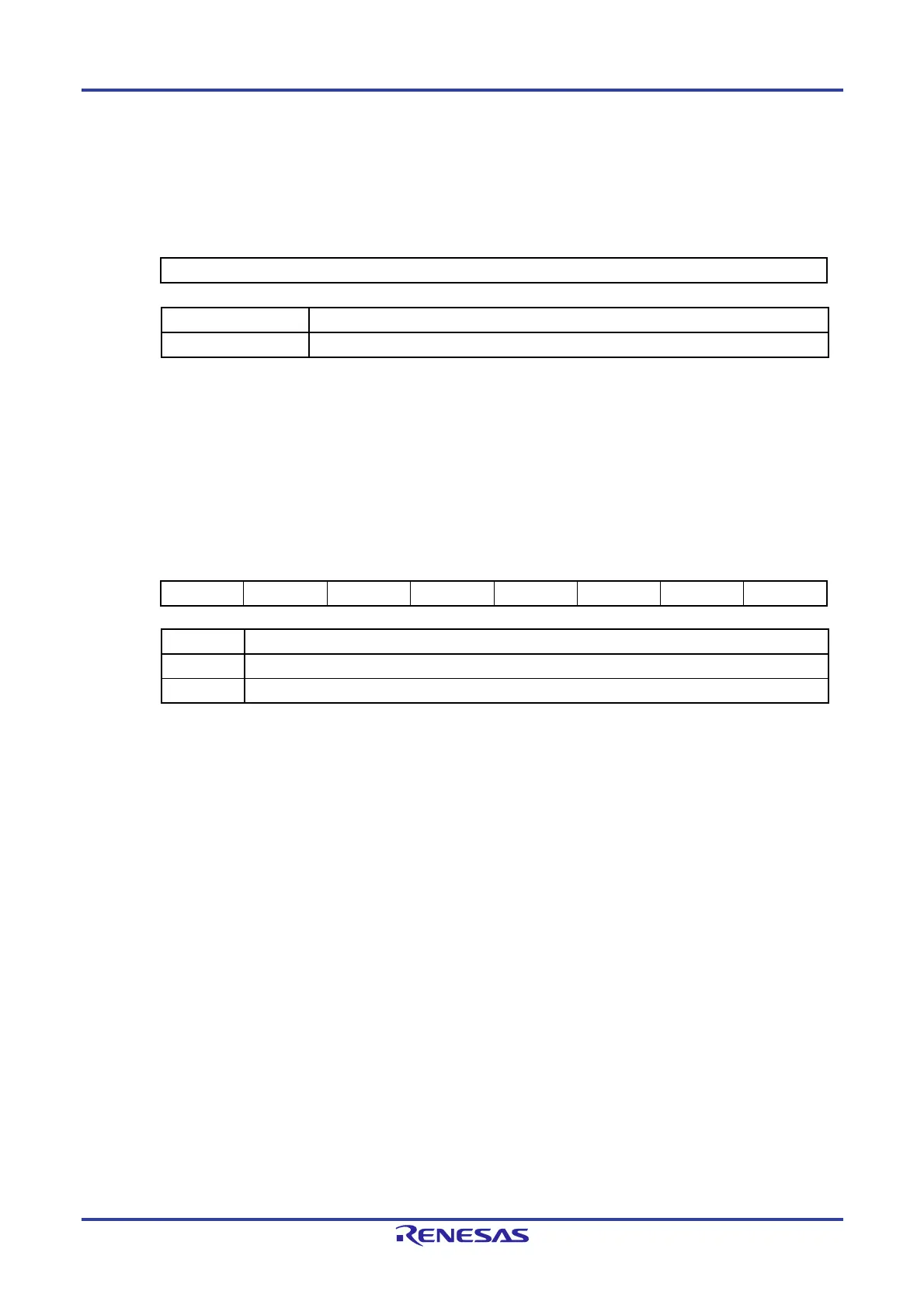

(1) Error address store register (ERADR)

Figure 27-8. Format of Error Address Store Register (ERADR)

Address: F0200H After reset: 00H R/W

Symbol 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ERADR ERAD

ERAD Bit error address

0000H to FFFFH Address when a bit error interrupt request is generated

Cautions 1. Access the ERADR register in word units.

2. The register value is updated each time a bit error interrupt request is generated.

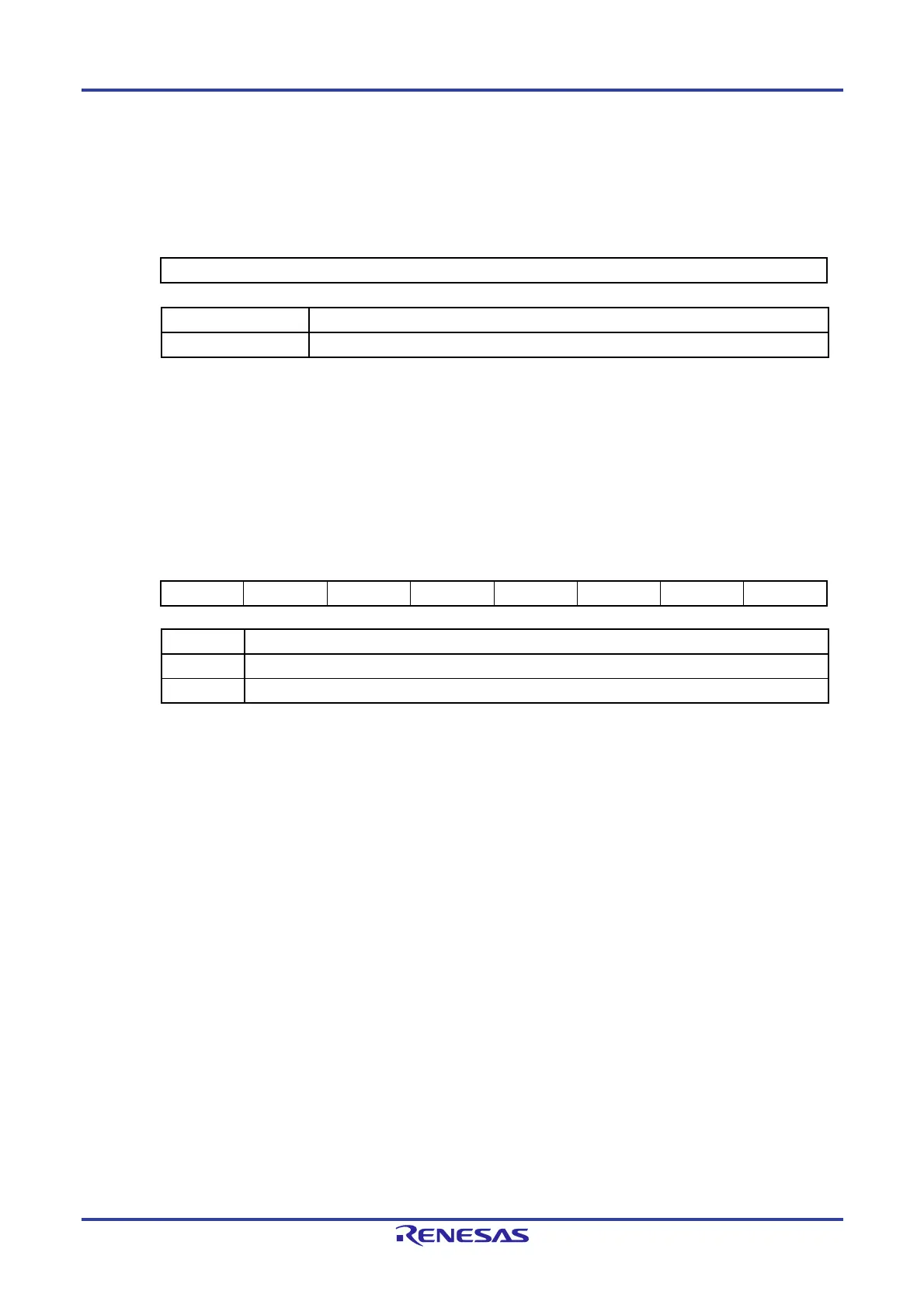

(2) 1-bit error detection interrupt enable register (ECCIER)

Figure 27-9. Format of 1-bit Error Detection Interrupt Enable Register (ECCIER)

Address: F0202H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

ECCIER - - - - - - - IEN

IEN 1-bit error detection interrupt enable bit

0 Interrupt disabled

1 Interrupt enabled

Cautions 1. Bits 1 to 7 of the ECCIER register are always read as 0. The write value should always be

0.

2. INTRAM interrupt request occurs regardless of the value of ECCIER on two bits error.

<R>

Loading...

Loading...