4-6 Loss-of-Potential, Load Encroachment, and Directional Element Logic Date Code 20001006

SEL-351 Instruction Manual

Apply Load-Encroachment Logic to a Phase Time-Overcurrent

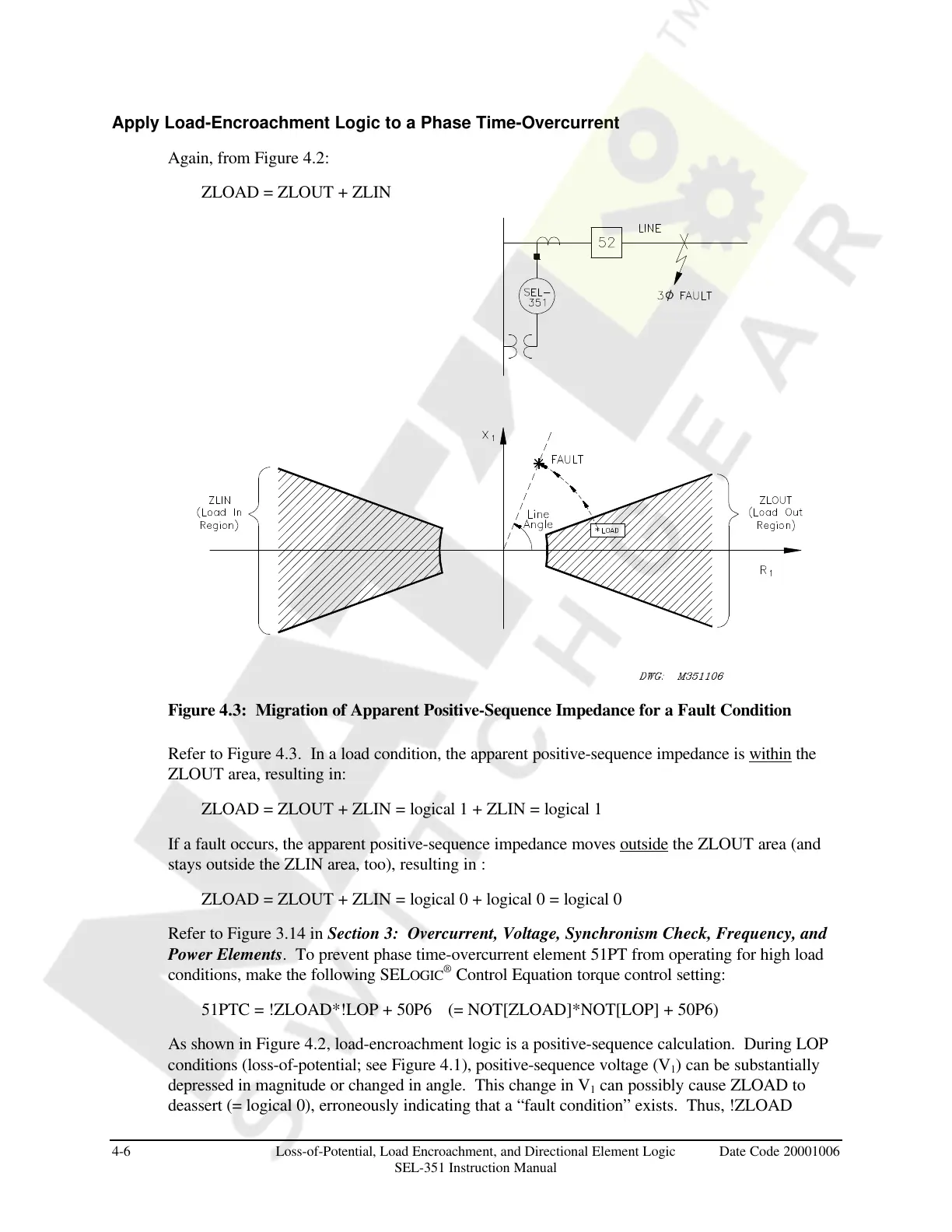

Again, from Figure 4.2:

ZLOAD = ZLOUT + ZLIN

Figure 4.3: Migration of Apparent Positive-Sequence Impedance for a Fault Condition

Refer to Figure 4.3. In a load condition, the apparent positive-sequence impedance is within the

ZLOUT area, resulting in:

ZLOAD = ZLOUT + ZLIN = logical 1 + ZLIN = logical 1

If a fault occurs, the apparent positive-sequence impedance moves outside the ZLOUT area (and

stays outside the ZLIN area, too), resulting in :

ZLOAD = ZLOUT + ZLIN = logical 0 + logical 0 = logical 0

Refer to Figure 3.14 in Section 3: Overcurrent, Voltage, Synchronism Check, Frequency, and

Power Elements. To prevent phase time-overcurrent element 51PT from operating for high load

conditions, make the following SELOGIC

®

Control Equation torque control setting:

51PTC = !ZLOAD*!LOP + 50P6 (= NOT[ZLOAD]*NOT[LOP] + 50P6)

As shown in Figure 4.2, load-encroachment logic is a positive-sequence calculation. During LOP

conditions (loss-of-potential; see Figure 4.1), positive-sequence voltage (V

1

) can be substantially

depressed in magnitude or changed in angle. This change in V

1

can possibly cause ZLOAD to

deassert (= logical 0), erroneously indicating that a “fault condition” exists. Thus, !ZLOAD

Courtesy of NationalSwitchgear.com

Loading...

Loading...