12-18 Standard Event Reports, Sag/Swell/Interruption Report, and SER Date Code 20001006

SEL-351 Instruction Manual

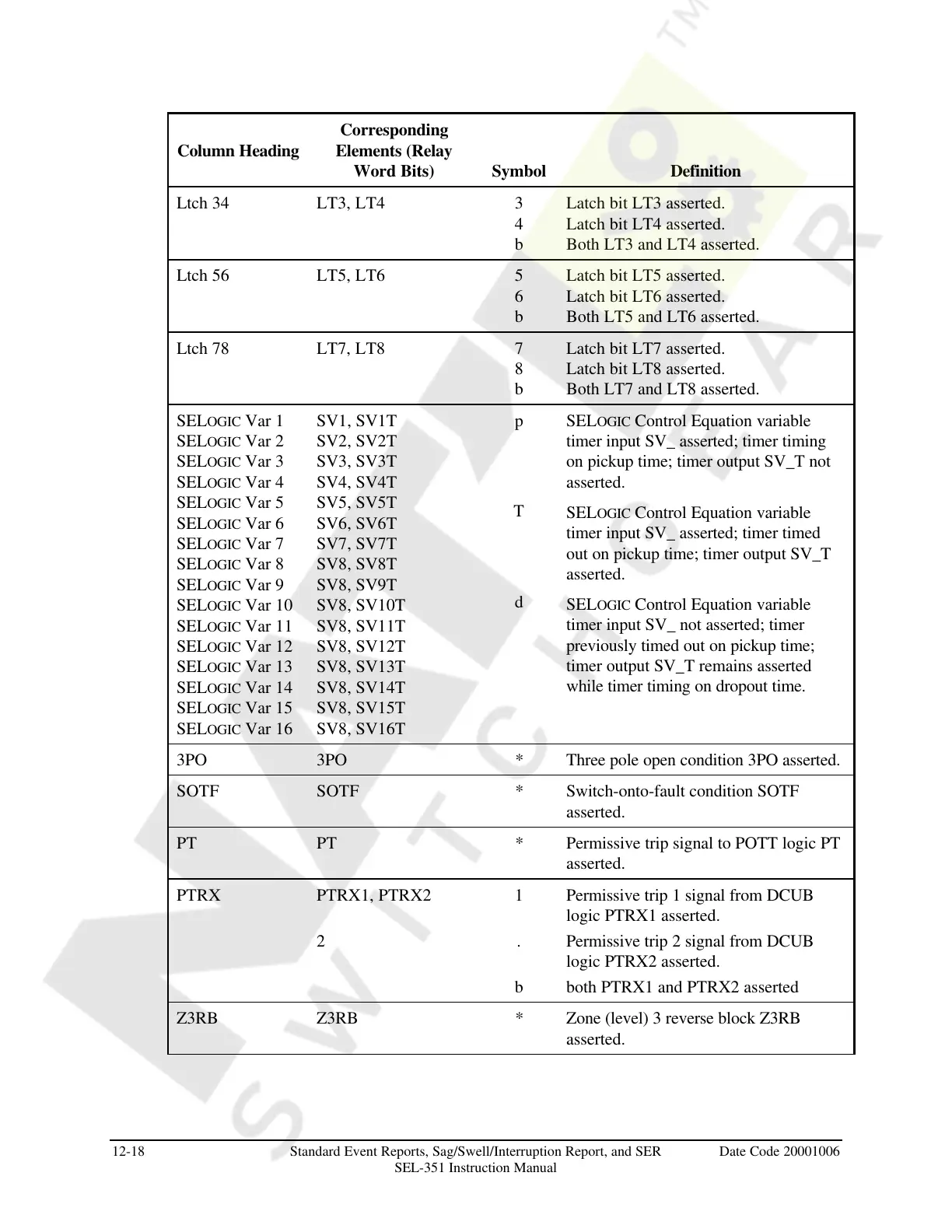

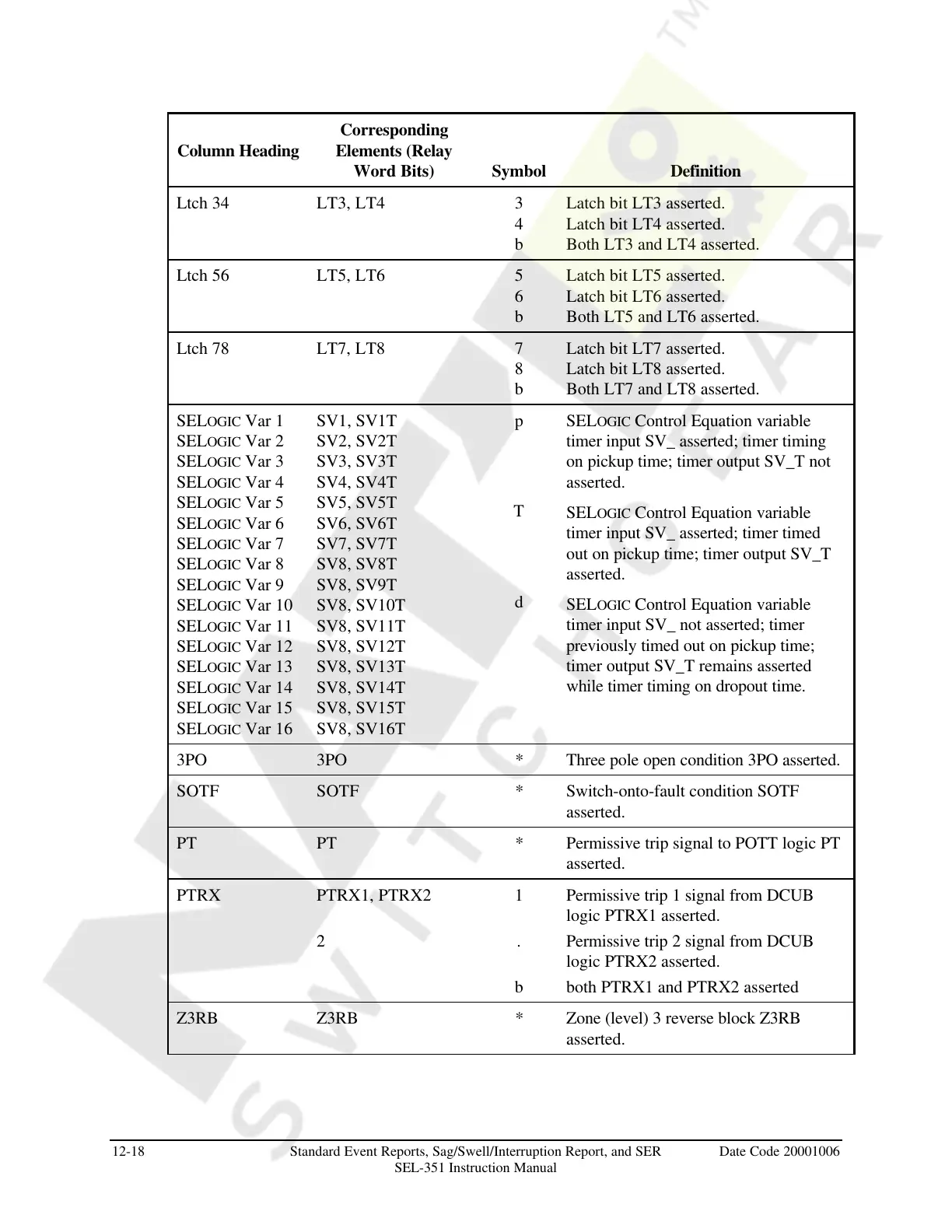

Column Heading

Corresponding

Elements (Relay

Word Bits) Symbol Definition

Ltch 34 LT3, LT4 3 Latch bit LT3 asserted.

4 Latch bit LT4 asserted.

b Both LT3 and LT4 asserted.

Ltch 56 LT5, LT6 5 Latch bit LT5 asserted.

6 Latch bit LT6 asserted.

b Both LT5 and LT6 asserted.

Ltch 78 LT7, LT8 7 Latch bit LT7 asserted.

8 Latch bit LT8 asserted.

b Both LT7 and LT8 asserted.

SELOGIC Var 1

SELOGIC Var 2

SELOGIC Var 3

SELOGIC Var 4

SELOGIC Var 5

SELOGIC Var 6

SELOGIC Var 7

SELOGIC Var 8

SELOGIC Var 9

SELOGIC Var 10

SELOGIC Var 11

SELOGIC Var 12

SELOGIC Var 13

SELOGIC Var 14

SELOGIC Var 15

SELOGIC Var 16

SV1, SV1T

SV2, SV2T

SV3, SV3T

SV4, SV4T

SV5, SV5T

SV6, SV6T

SV7, SV7T

SV8, SV8T

SV8, SV9T

SV8, SV10T

SV8, SV11T

SV8, SV12T

SV8, SV13T

SV8, SV14T

SV8, SV15T

SV8, SV16T

p

T

d

SELOGIC Control Equation variable

timer input SV_ asserted; timer timing

on pickup time; timer output SV_T not

asserted.

SELOGIC Control Equation variable

timer input SV_ asserted; timer timed

out on pickup time; timer output SV_T

asserted.

SELOGIC Control Equation variable

timer input SV_ not asserted; timer

previously timed out on pickup time;

timer output SV_T remains asserted

while timer timing on dropout time.

3PO 3PO * Three pole open condition 3PO asserted.

SOTF SOTF * Switch-onto-fault condition SOTF

asserted.

PT PT * Permissive trip signal to POTT logic PT

asserted.

PTRX PTRX1, PTRX2 1 Permissive trip 1 signal from DCUB

logic PTRX1 asserted.

2 . Permissive trip 2 signal from DCUB

logic PTRX2 asserted.

b both PTRX1 and PTRX2 asserted

Z3RB Z3RB * Zone (level) 3 reverse block Z3RB

asserted.

Courtesy of NationalSwitchgear.com

Loading...

Loading...