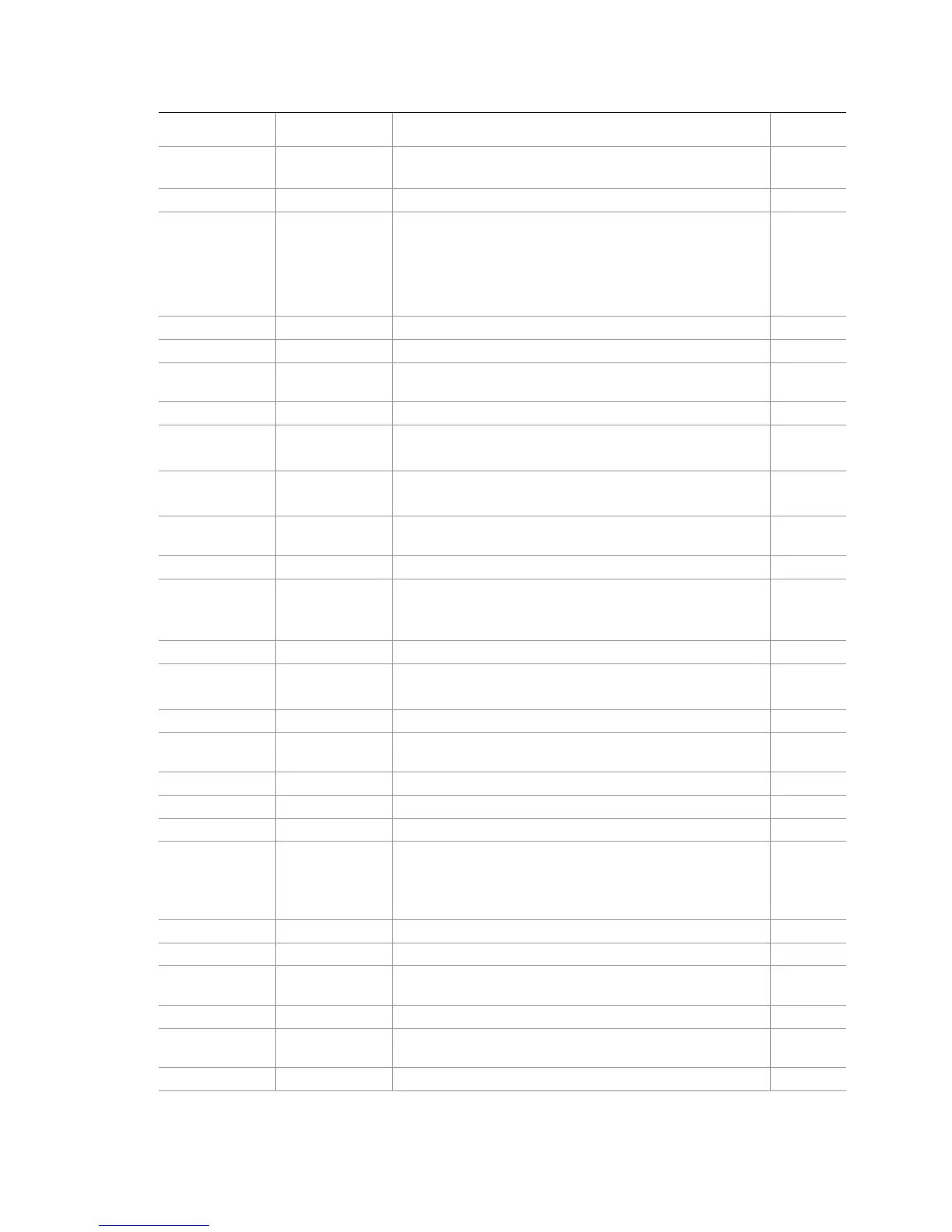

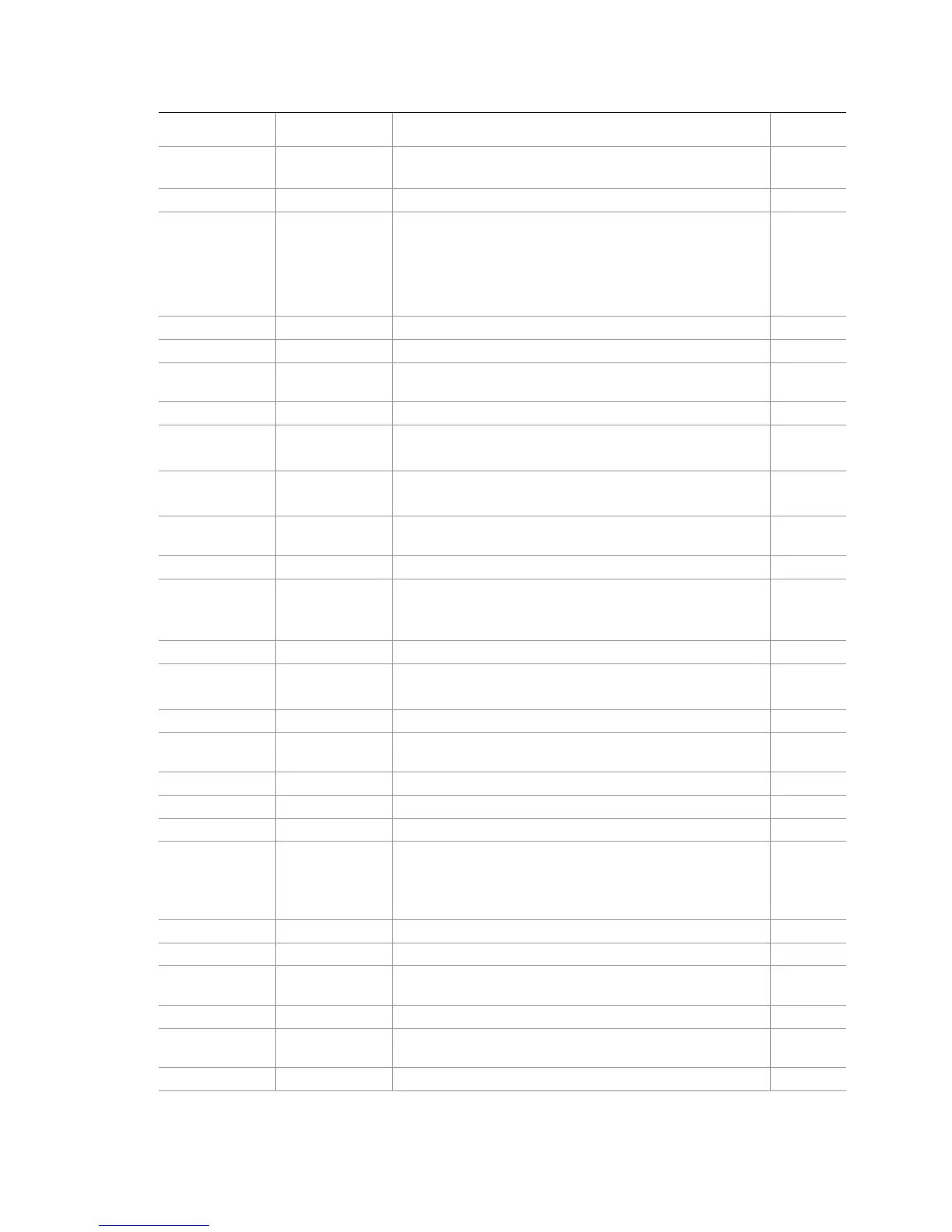

218

Code Number BSP, APs,

Both

Meaning Display

(sal_efi_module_15) size, align, and scratch buff size.

Initialize scratch buffer.

0x07EC BSP only Hang if ERROR. South

0x87EB BSP only

Save maximum (PAL,EFI) shadow size and alignment.

Save PAL(ia32)/EFI shadow top address, size,

alignment. EFI module shadow base address

(virtual/Physical), size, bottom address

(DATA+SAL+PAL+EFI). Update virtual address entries

in translation register descriptor, addresses in MDT,

South

0x87EA BSP+APs Cache flush shadow. South

0x07EA BSP + APs Hang on ERROR. South

0x87E9 BSP + APs

PAL call for memory Test for SELF

TEST(pal_mem_for_test_25).

South

0x07E9 BSP + APs Hang, if Memory ERROR. South

0x87E8 BSP + APs PAL call for PAL test (pal_test_proc_102)

and save results.

South

0x07E8 BSP + APs Hang, if late self test ERROR

NOTE: this can be skipped by a build switch.

South

0x87E7 BSP + APs

PAL Call for pal_bus_get_features function #

(pal_bus_get_features_09).

South

0x07E7 BSP + APs Hang if ERROR. South

0x87E6 BSP + APs Set buslock mask=1 (non-atomic)

By PAL Call PAL Bus Set Feature

(pal_bus_set_features_0a).

South

0x07E6 BSP + APs Hang if ERROR. South

0x87E5 BSP + APs Set PMI entry point

PAL Call (pal_pmi_entrypoint_20).

South

0x07E5 BSP + APs Hang if ERROR. South

0x87E4 BSP + APs

PAL Cache Summary by PAL Call

(pal_cache_summary_04).

South

0x07E4 BSP + APs Hang if ERROR South

0x87E3 BSP + APs PAL Cache Information set. PAL Call cache_info_02. South

0x07E3 BSP + APs Hang, if ERROR. South

0x87E2 BSP + APs pal_mc_register_mem_1b/find CPU min state pointer.

Should be able now to initialize health,bsp/ap,cache size

line size, sapic ver, and cpuid. Set minimal state save

area, BSPSTORE and SP.

South

0x87E1 BSP + APs Cache flush shadow. South

0x07E1 BSP + APs Hang if ERROR. South

0x87E0 BSP + APs

Program IVA, ITR(0) for PAL,SAL runtime code & data

area cr.iva/cr.ifa/cr.itir/itr[r0].

South

0x87DF BSP + APs Clear semaphore and wait for all CPUs to synchronize. South

0x87DE BSP + APs

Sort CPU health. Already sorted for 2nd level BSP

selection. Store BSP/AP flag for respective CPU.

South

0x87DD APs

Setup for interrupt wakeup reinitialization of BSPSTORE

South

Loading...

Loading...