223

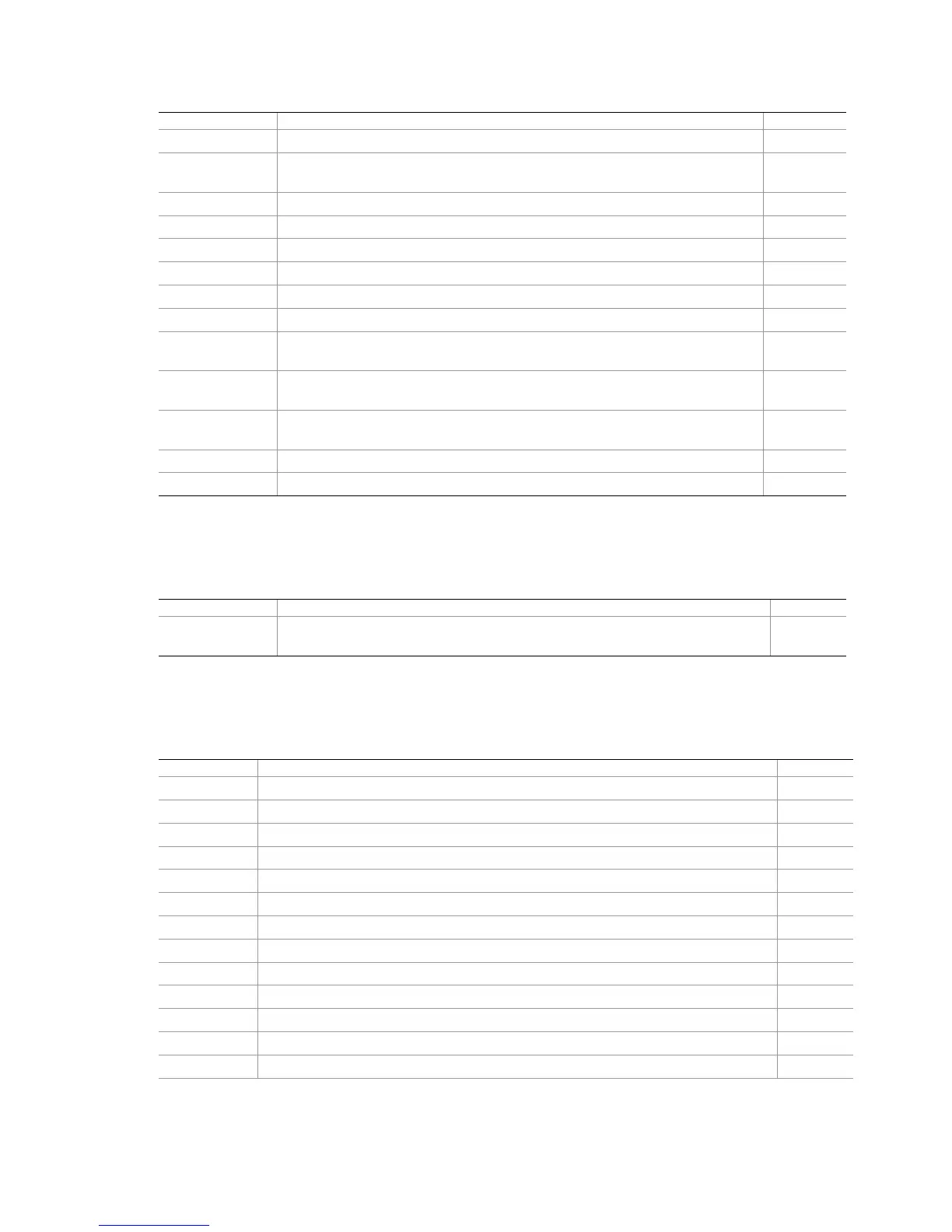

Code Value Module Display

0x00A5 Memory wait state programming is over. Clearing the screen. South

0x00A7

Performing any initialization required before passing control to the adaptor

ROM at E000 next.

South

0x00AE Setting up DMI structures. South

0x0020 Talking to BMC South

0x0022 Talking to BMC. South

0x00AC Uncompressing the DMI data and initializing DMI POST. South

0x00AB Building the multiprocessor table. South

0x00AD Prepare INT10 image. Update the necessary data in different modules. South

0x00A8

Initialization before passing control to the adaptor ROM at E000h

completed. Pass control to the adaptor ROM at E000h.

South

0x00A9

Returned from adaptor ROM at E000h control. Performing any

initialization required after the E000 option ROM had control next.

South

0x00AA

Initialization after E000 option ROM control has completed. Displaying the

system configuration.

South

0x00B1 Copying any runtime code to specific areas. South

0x0000 Code copying to specific areas is done. Pass control to EFI. South

Table 46. ACPI POST Codes

Code Value Module Display

0x0400 –

0x04FF

Reserved for ACPI South

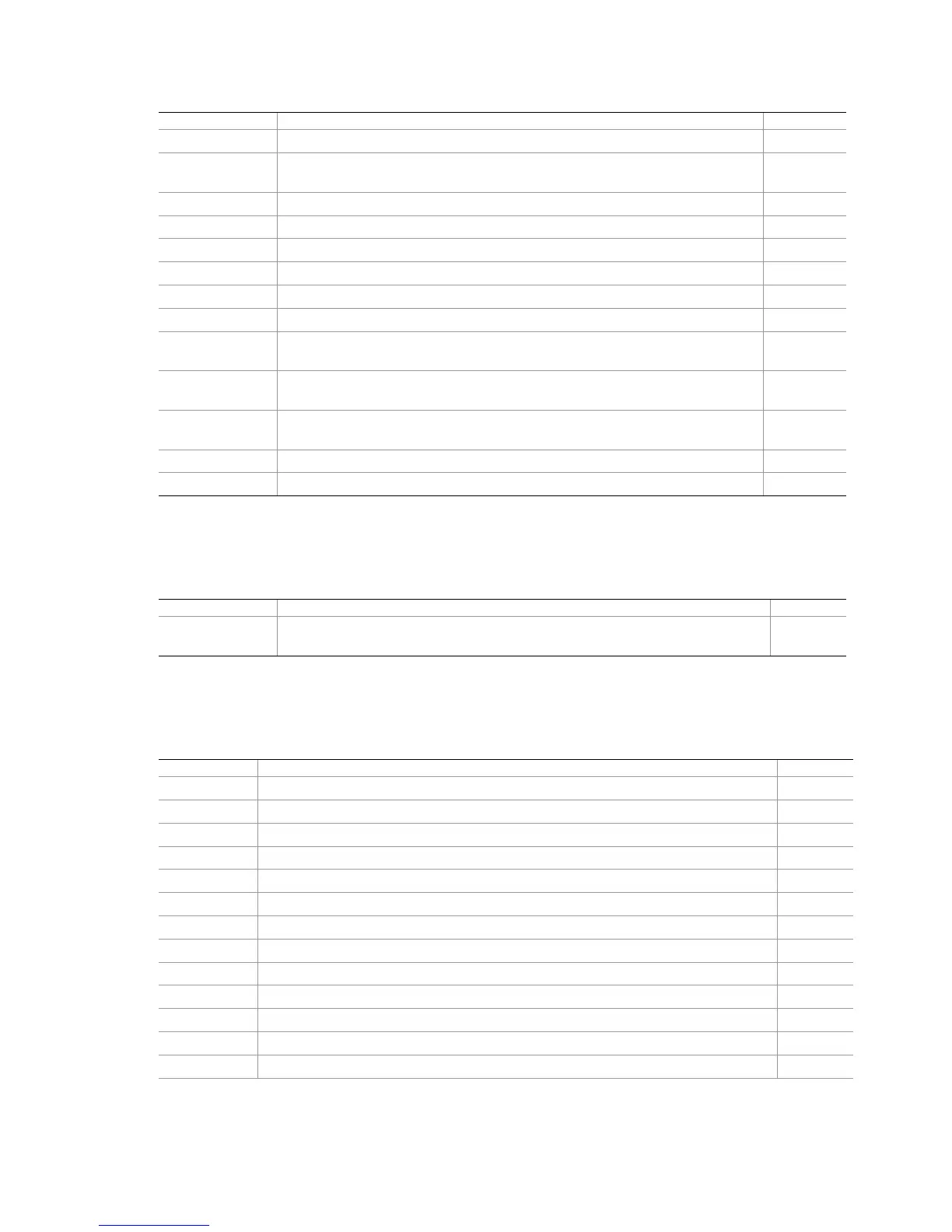

Table 47. SAL Runtime POST Codes

Code Value Module Display

0xAFCD IA-32 Intercept Trap due to an unsupported IA-32 instruction South

0xAFE8 Normal SAL Machine Check Handling in Progress South

0xAFE9 Could Not Correct MC Error, Halting CPU South

0xAFEA MCA successfully completed, passing control back to PAL (Resume) South

0xAFEB Calling OS MCA for Machine Check error handling South

0xAFEC Machine Check Handler Processing Rendezvous Request South

0xAFED OS request for SAL Clear Processor/Platform Error/State Log in progress South

0xAFEE SAL Platform OEM MCA Error Handler In Control South

0xAFEF OS request for SAL Get Processor/Platform Error/State Log in progress South

0xAFF0 SAL INIT Handler is in control South

0xAFF1 Passing Control to IA-32 OS Init Handler South

0xAFF2 Found valid OS_INIT Ep, Passing Control to EM OS Init Handler South

0xAFF3 Is a MP platform MCA condition, calling SAL_RENDZ South

Loading...

Loading...