Titanium Interfaces User Guide

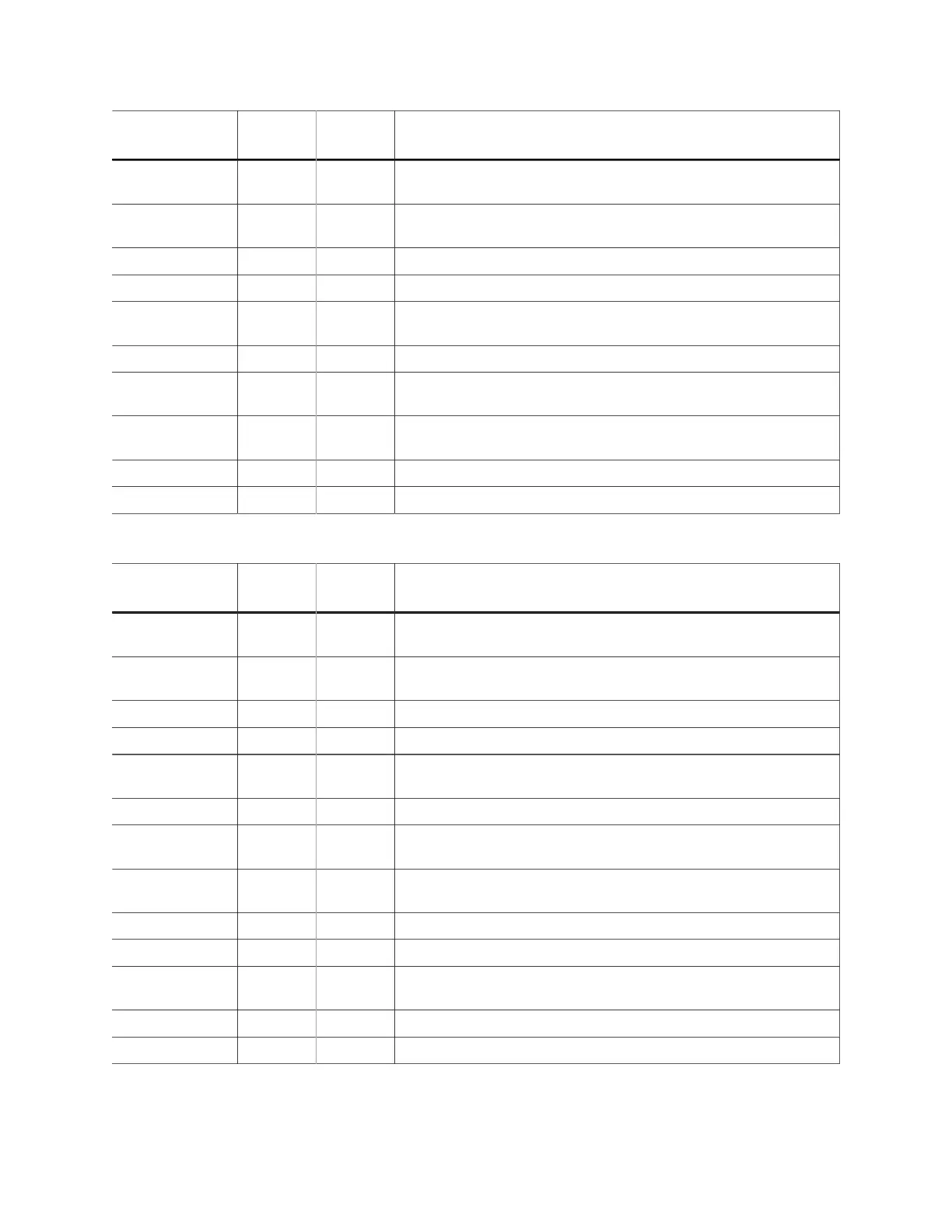

Table 19: AXI4 Read Address Signals (Interface to FPGA Fabric)

Signal

x is 0 or 1

Direction Clock

Domain

Description

ARADDR_x[31:0] Input ACLK_x Read address. It gives the address of the first transfer in a burst

transaction.

ARBURST_x[1:0] Input ACLK_x Burst type. The burst type and the size determine how the address

for each transfer within the burst is calculated.

ARID_x[5:0] Input ACLK_x Address ID. This signal identifies the group of address signals.

ARLEN_x[7:0] Input ACLK_x Burst length. This signal indicates the number of transfers in a burst.

ARREADY_x Output ACLK_x Address ready. This signal indicates that the slave is ready to accept

an address and associated control signals.

ARSIZE_x[2:0] Input ACLK_x Burst size. This signal indicates the size of each transfer in the burst.

ARVALID_x Input ACLK_x Address valid. This signal indicates that the channel is signaling

valid address and control information.

ARLOCK_x Input ACLK_x Lock type. This signal provides additional information about the

atomic characteristics of the transfer.

ARAPCMD_x Input ACLK_x Read auto-precharge.

ARQOS_x Input ACLK_x QoS indentifier for read transaction.

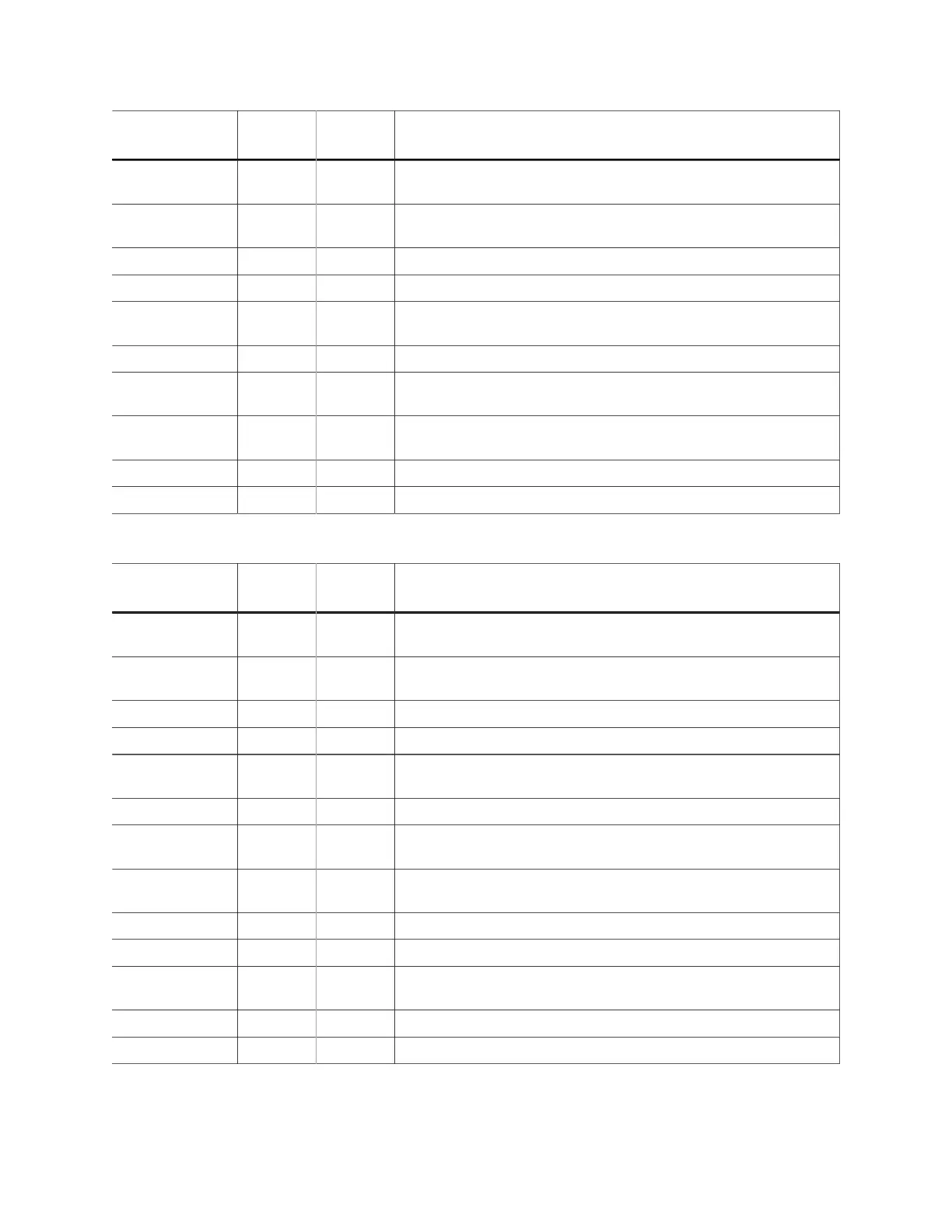

Table 20: AXI4 Write Address Signals (Interface to FPGA Fabric)

Signal

x is 0 or 1

Direction Clock

Domain

Description

AWADDR_x[31:0] Input ACLK_x Write address. It gives the address of the first transfer in a burst

transaction.

AWBURST_x[1:0] Input ACLK_x Burst type. The burst type and the size determine how the address

for each transfer within the burst is calculated.

AWID_x[5:0] Input ACLK_x Address ID. This signal identifies the group of address signals.

AWLEN_x[7:0] Input ACLK_x Burst length. This signal indicates the number of transfers in a burst.

AWREADY_x Output ACLK_x Address ready. This signal indicates that the slave is ready to accept

an address and associated control signals.

AWSIZE_x[2:0] Input ACLK_x Burst size. This signal indicates the size of each transfer in the burst.

AWVALID_x Input ACLK_x Address valid. This signal indicates that the channel is signaling

valid address and control information.

AWLOCK_x Input ACLK_x Lock type. This signal provides additional information about the

atomic characteristics of the transfer.

AWAPCMD_x Input ACLK_x Write auto-precharge.

AWQOS_x Input ACLK_x QoS indentifier for write transaction.

AWCACHE_x[3:0] Input ACLK_x Memory type. This signal indicates how transactions are required to

progress through a system.

AWALLSTRB_x Input ACLK_x Write all strobes asserted.

AWCOBUF_x Input ACLK_x Write coherent bufferable selection.

www.efinixinc.com 36

Loading...

Loading...