Titanium Interfaces User Guide

Table 37: Full and Half Rate Serialization

Mode Description Example

Full rate clock In full rate mode, the fast clock runs at

the same frequency as the data and

captures data on the positive clock

edge.

Data rate: 800 Mbps

Serialization/Deserialization factor: 8

Slow clock frequency: 100 Mhz (800 Mbps / 8)

Fast clock frequency: 800 Mhz

Half rate clock In half rate mode, the fast clock runs at

half the speed of the data and captures

data on both clock edges.

Data rate: 800 Mbps

Serialization / Deserialization factor: 8

Slow clock frequency: 100 Mhz (800 Mbps / 8)

Fast clock frequency: 400 Mhz (800 / 2 )

You use a PLL to generate the serial (fast) and parallel (slow) clocks for the LVDS pins. The

slow clock runs at the data rate divided by the serialization factor.

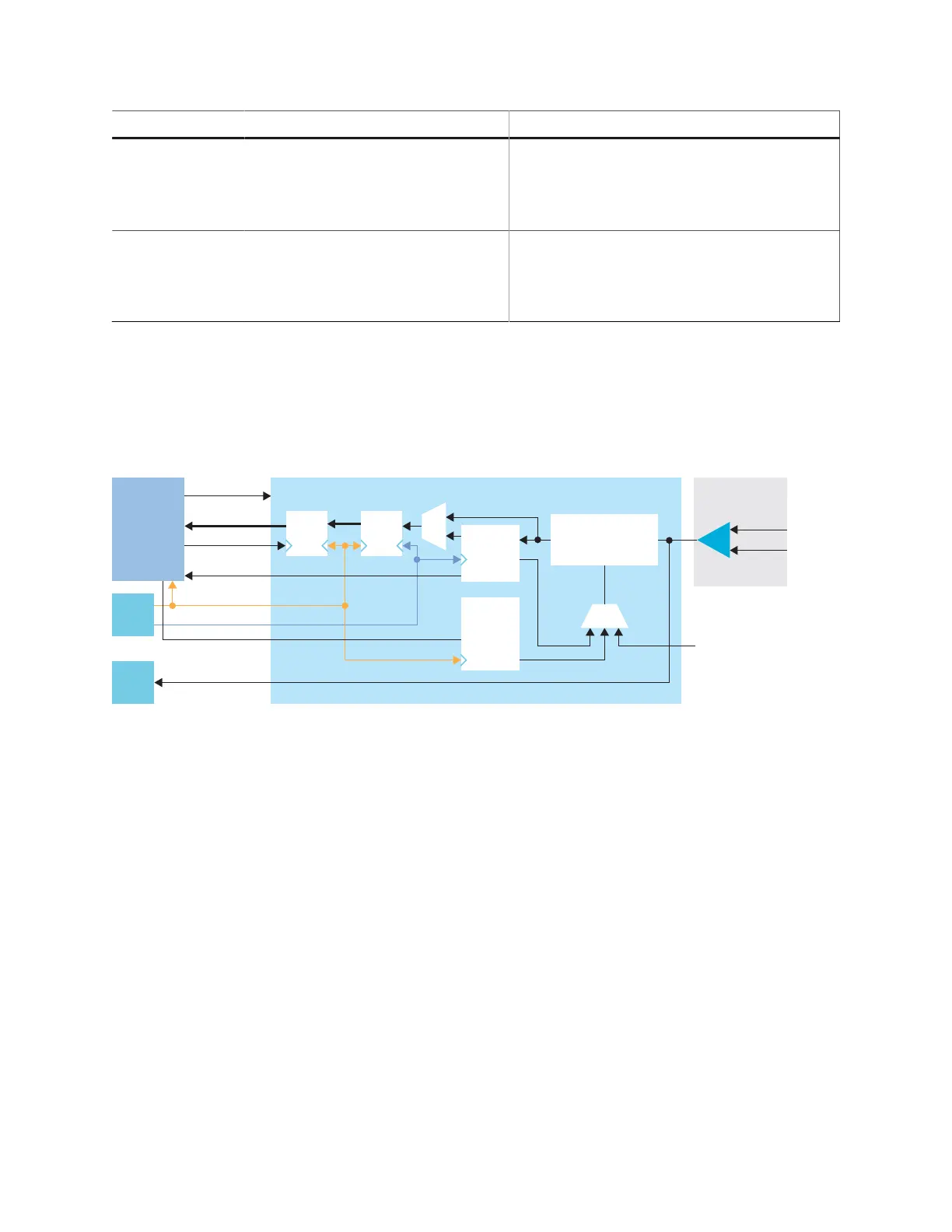

LVDS RX

You can configure an HSIO block as one LVDS RX signal.

Figure 22: LVDS RX Interface Block Diagram

LOCK

Up/

Down

Counter

Configuration

Setting

www.efinixinc.com 68

Loading...

Loading...