ES910.3-A - User’s Guide 82

ETAS Technical Data

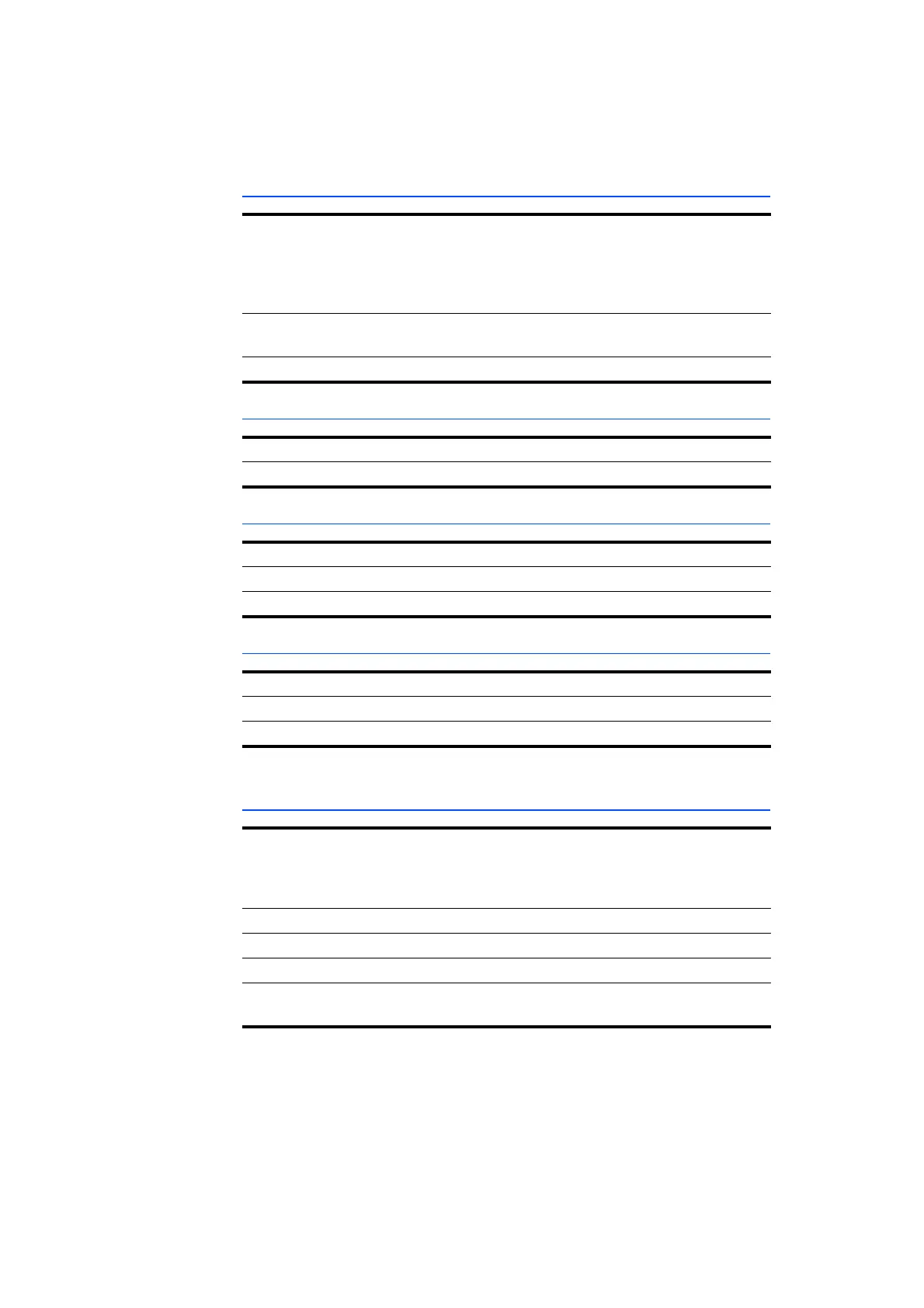

7.7.4 CAN Interfaces (CAN1/LIN1 and CAN2/LIN2)

Low-Speed CAN

High-Speed CAN

High-Speed CAN “Wake Up” Signal Conditions

At least two signal edges of the same polarity must be within a period of 100 ms.

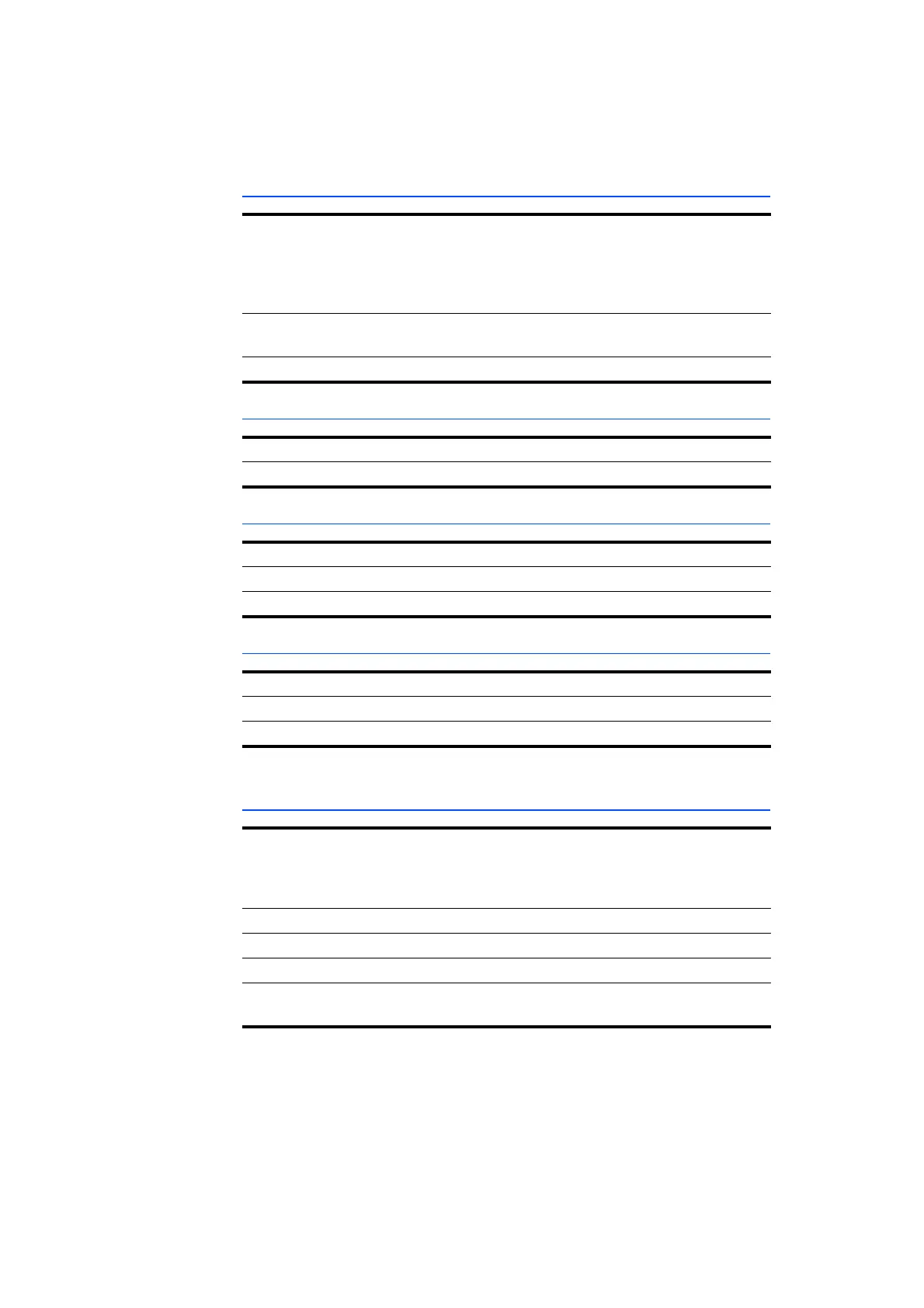

7.7.5 LIN Interfaces (CAN1/LIN1 and CAN2/LIN2)

CAN1 to CAN2 2 independent interfaces,

galvanically isolated from each other and

from the other interfaces,

every channel separately configurable

(High-Speed CAN and Low-Speed CAN)

Protocols CAN V2.0a (Standard Identifier),

CAN V2.0b (Extended Identifier)

Controller IP-Core (FPGA)

Transceiver (Physical Layer) TJA1054

Transfer speed Max. 125 kBaud

Transceiver (Physical Layer) TJA1040

Transfer speed Max. 1 MBaud with a bus length of 20 m

Differential internal resistor Ri 10 kOhm

Differential input voltage (min.) V_diff,min = 0.2 V

Signal edge increase rate t/dV < 150 ns/V

Differential input resistor R i,diff = 10 kOhm

LIN1 to LIN2 2 independent interfaces,

galvanically isolated from each other and

from the other interfaces,

every channel separately configurable

Specification LIN V2.1

Controller LIN-Core (FPGA)

Transceiver (Physical Layer) MCZ33661EF

Operating mode Master or Slave (configurable in the

ES910.3-A web interface)

Loading...

Loading...