Address Setting

The address of the module during the slave mode will be stored in the I²C Bus Address Register

(IBAD) on the 7-bit field ADR.

Transfer setting

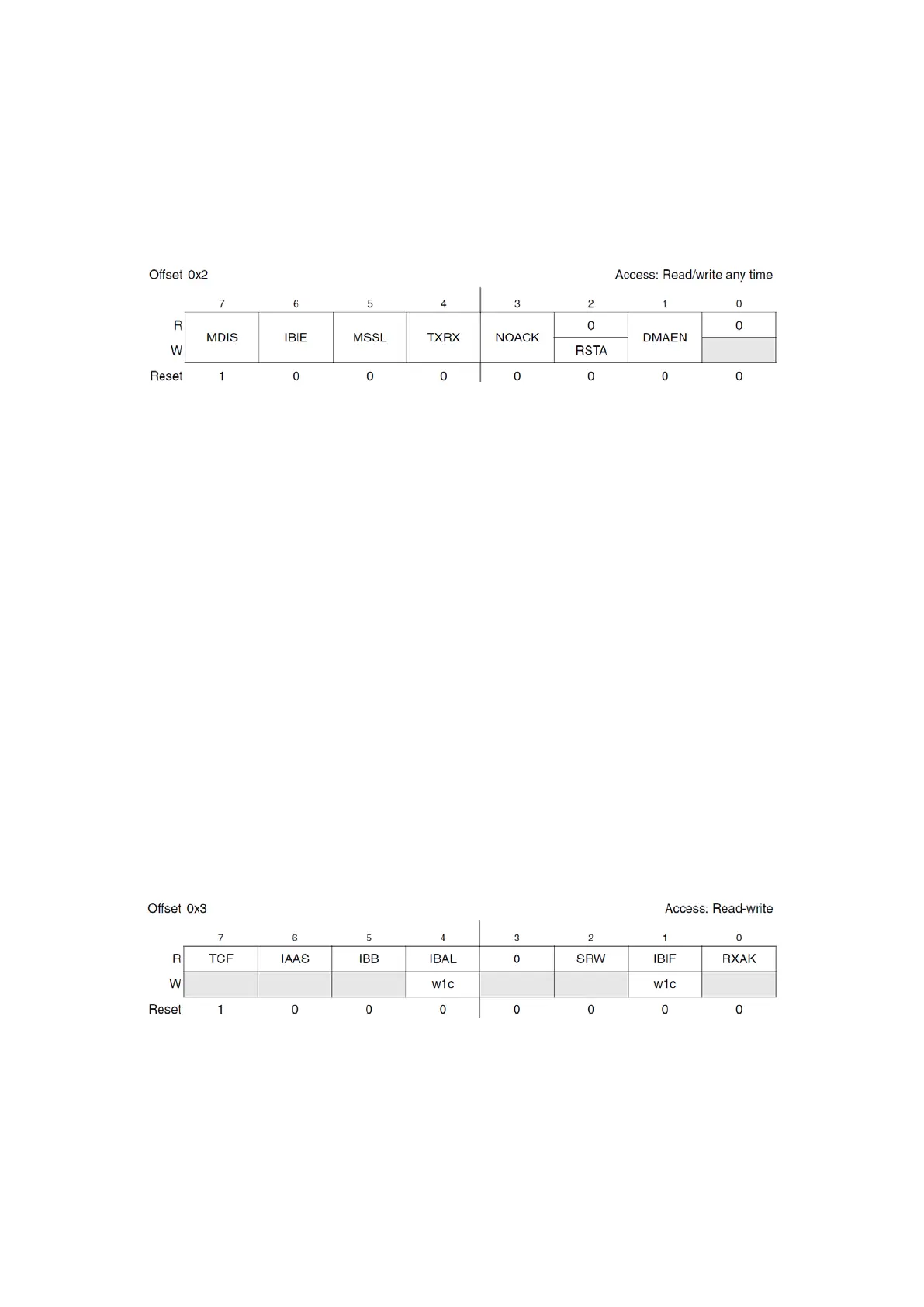

For configuring various aspects of the module, I²C BUS Control Register (IBCR) can be used.

Figure 107 : I²C Bus Control Register (R.M. Rev8 – Fig. 20-6)

Details about modifiable fields of this register:

o MDIS: Module Disable, this bit is set on reset and it has to be cleared before using

this module.

o IBIE: I-Bus Interrupt Enable, I²C interrupts are enabled, related to the flag IBIF

on the status register.

o MSSL: Master/Slave mode select, 0 for slave and 1 for master. On a change from

0 to 1, a START signal is automatically generated and on the reverse change, a

STOP signal will be generated. This bit is automatically cleared if the master loses

arbitration.

o TXRX: Transmit/Receive mode select, 1 for transmit. When operating as a slave,

this bit should be set according to the demands of the master, and when

operating as a master, it is used during the address cycle for informing the slave.

o NOACK: Data Acknowledge Disable, when this bit is set, no acknowledge signal

will be sent. Used for stopping communication when reading as a master.

o RSTA: Repeat Start, when 1 is written to this bit, a repeated START condition will

be generated. This can be used for changing TX/RX mode, but if it is used while

another master is controlling the bus, then a loss of arbitration will occur.

Status/Interrupt Management

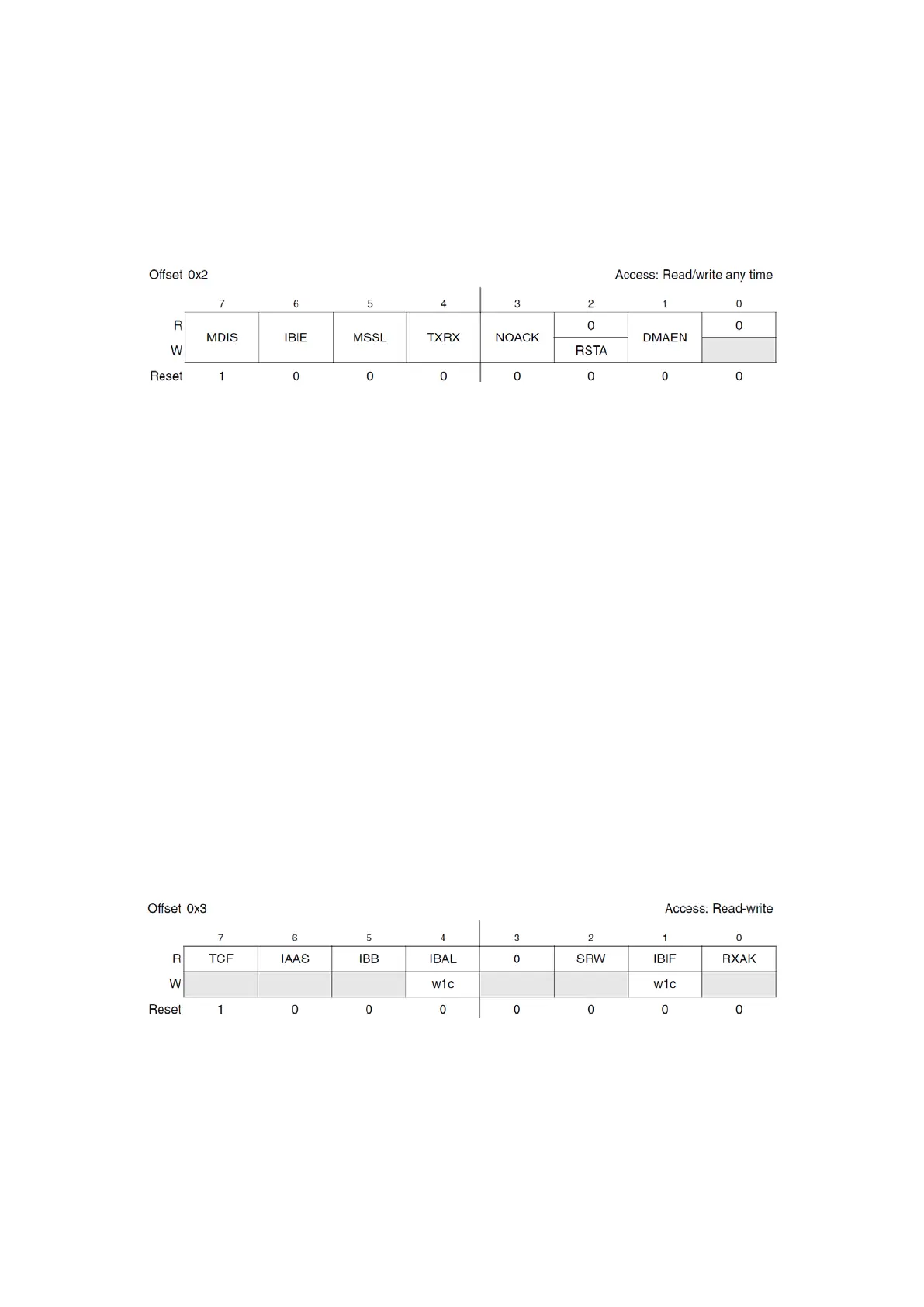

Figure 108 : I²C Bus Status Register (R.M. Rev8 – Fig. 20-6)

The I²C Bus Status Register (IBSR) contains flags that are useful during communication in order

to determine the next set of actions. Different bits are:

TCF: Transfer Complete flag, when 0, a transfer is in progress and when at high a transfer

is complete. (It is at ‘1’ by default).

Loading...

Loading...