Without making any channel configurations, this block can be seen as multiple 16-bit up-

counting channels that can select a counter among its internal counter, the 16-bit counter bus A

or one of 16-bit counter busses B, C, D or E, depending on the channel’s position.

Each of these counter busses are controlled by one particular channel configured as a counter,

previous figure shows that bus A is controlled by channel 23 and B, C, D and E are respectively

controlled by channels 0, 8, 16 and 24. Each channel contains four internal 16-bit registers A1,

B1, A2, and B2 that are used for implementing different behaviours.

Each eMIOS module has four general configuration registers:

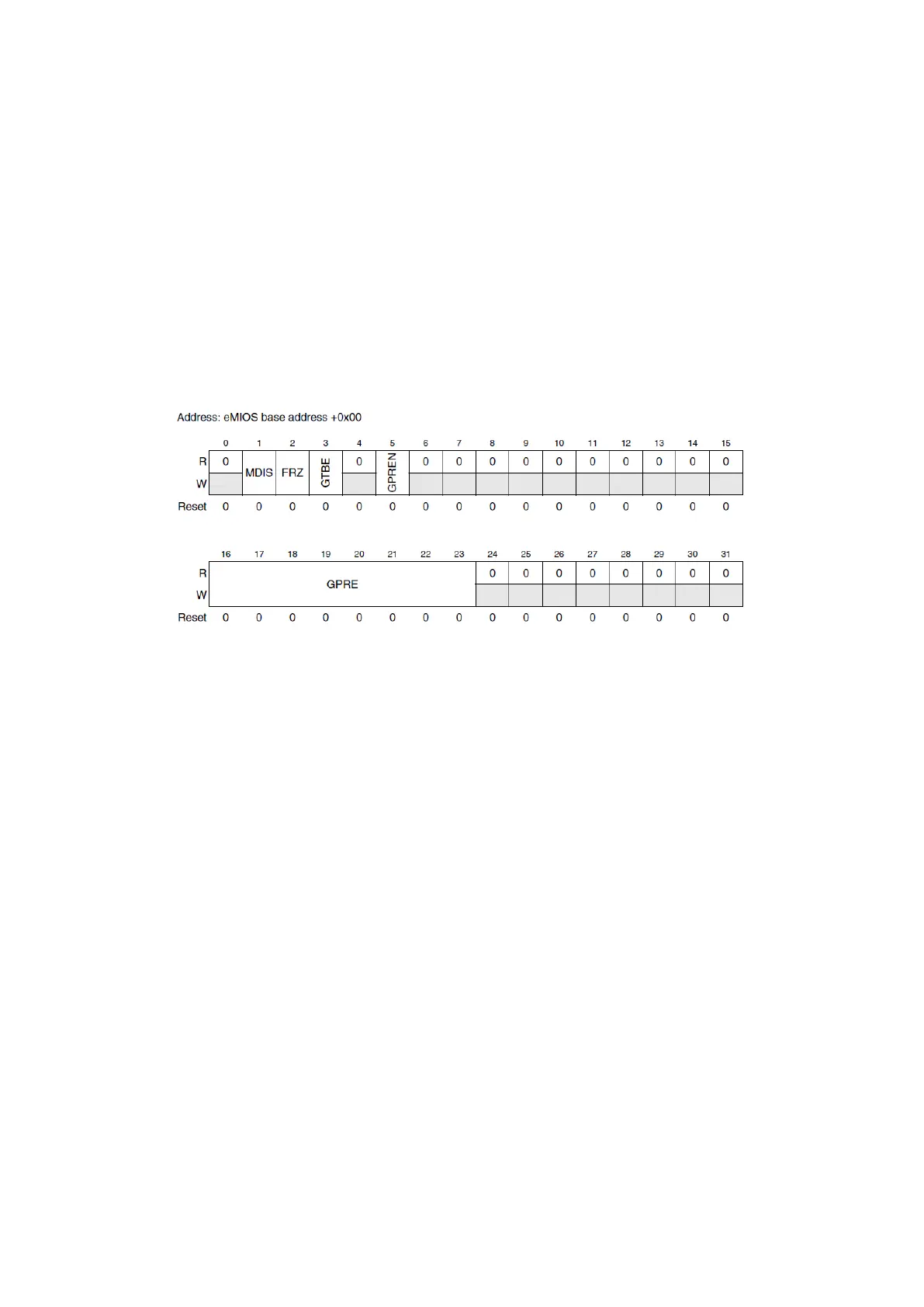

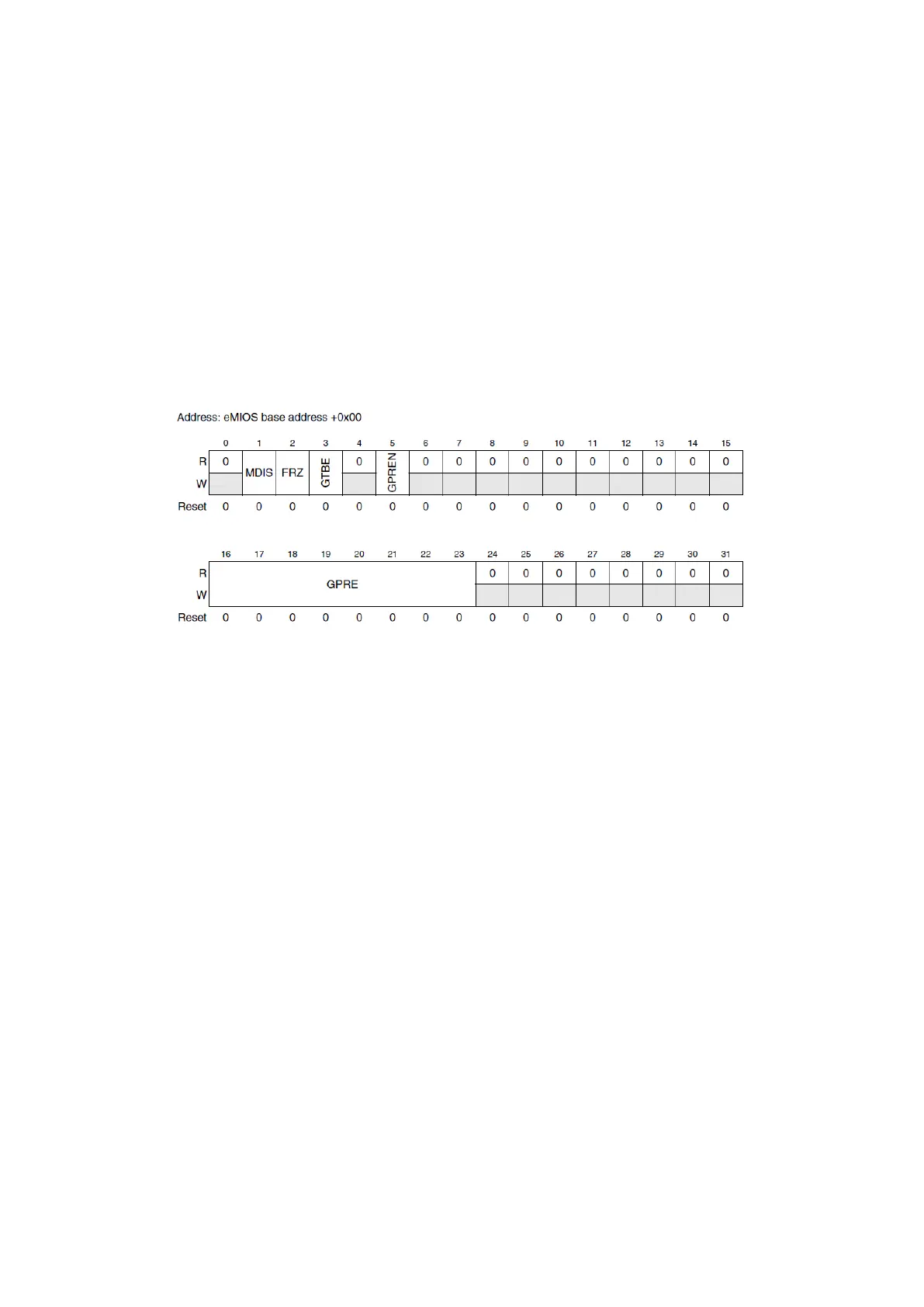

Figure 44 : eMIOS Module Configuration Register (R.M. Rev8 – Fig. 24-8)

EMIOS_MCR register has a Module Disable (MDIS) bit to put the block in low power mode when

set, a Freeze (FRZ) bit to freeze each channel in debug mode, which would allow better

debugging. Global Time Base Enable (GTBE) bit is for enabling the global 8-bit counter of the

eMIOS module, Global Prescaler Enable(GPREN) bit disables the clock when set to ‘0’ and

divides the clock of the ‘peripheral set 3’ by Global Prescaler (GPRE+1) when set to ‘1’ (so, the

peripheral clock can be divided up to 256).

Another important register is the eMIOS Global Flag Register (EMIO_GFR), which contains a flag

bit per each 28 channel of the block (F0 … F27). This is a read only register.

eMIOS Disable Channel Register (EMIOS_UCDIS) contains 28 disable bits for each channel

(CHDIS0 … CHDIS27), for disabling (setting to ‘1’) or enabling (clearing) them. Channels should

be all enabled by default.

When a channel is running in MC, MCB or an output mode, values written to A2 and B2 are

transferred to A1 and B2 (either immediately or in the next period). eMIOS Output Update

Disable Register (EMIOS_OUDR) contains 28 bits (OU0 … OU27) for disabling this data transfer

(when set to ‘1’).

Loading...

Loading...