Message buffer data coherence mechanisms:

Deactivation: when the user tries to write to the Control & Status word of an MB, the MB

will be excluded from the ongoing Tx/Rx arbitration/matching cycle. This will allow

maintaining some data coherency but there still some situations where incoherencies

can occur (see R.M Rev8, 22.4.7.2).

Lock: when user reads the Control & Status word of an Rx MB, it is assumed that user

wants to read the whole MB so its contents are locked, and cannot be altered until the

user makes a dummy read of the free-running timer (TIMER register) or until it reads

another MB’s Control & Status.

When FIFO option is selected the first eight message buffers in the memory is replaced by a FIFO

engine.

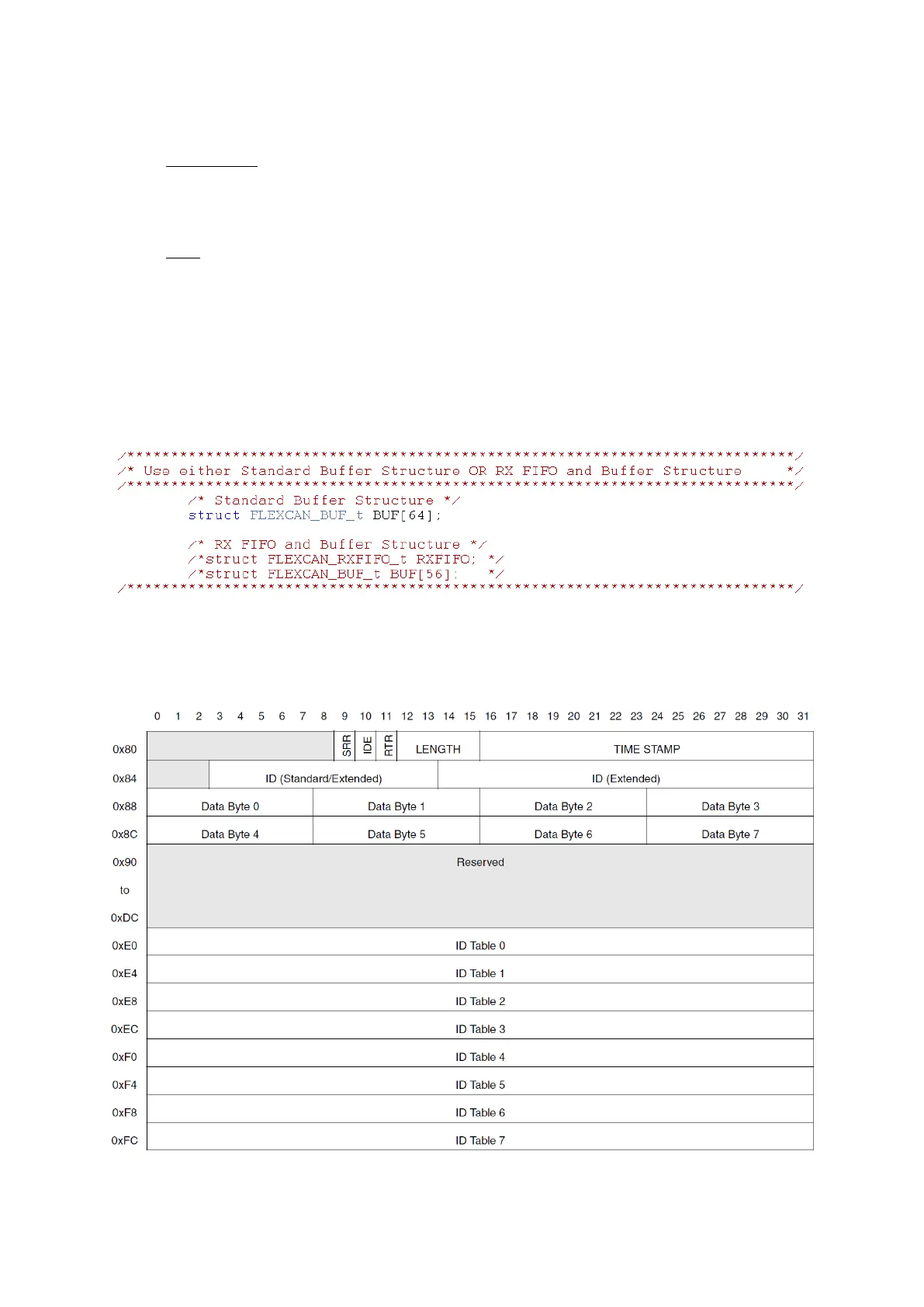

Figure 120: Selecting the memory mapping of FlexCAN in MPC5604B_0M27V_0102.h

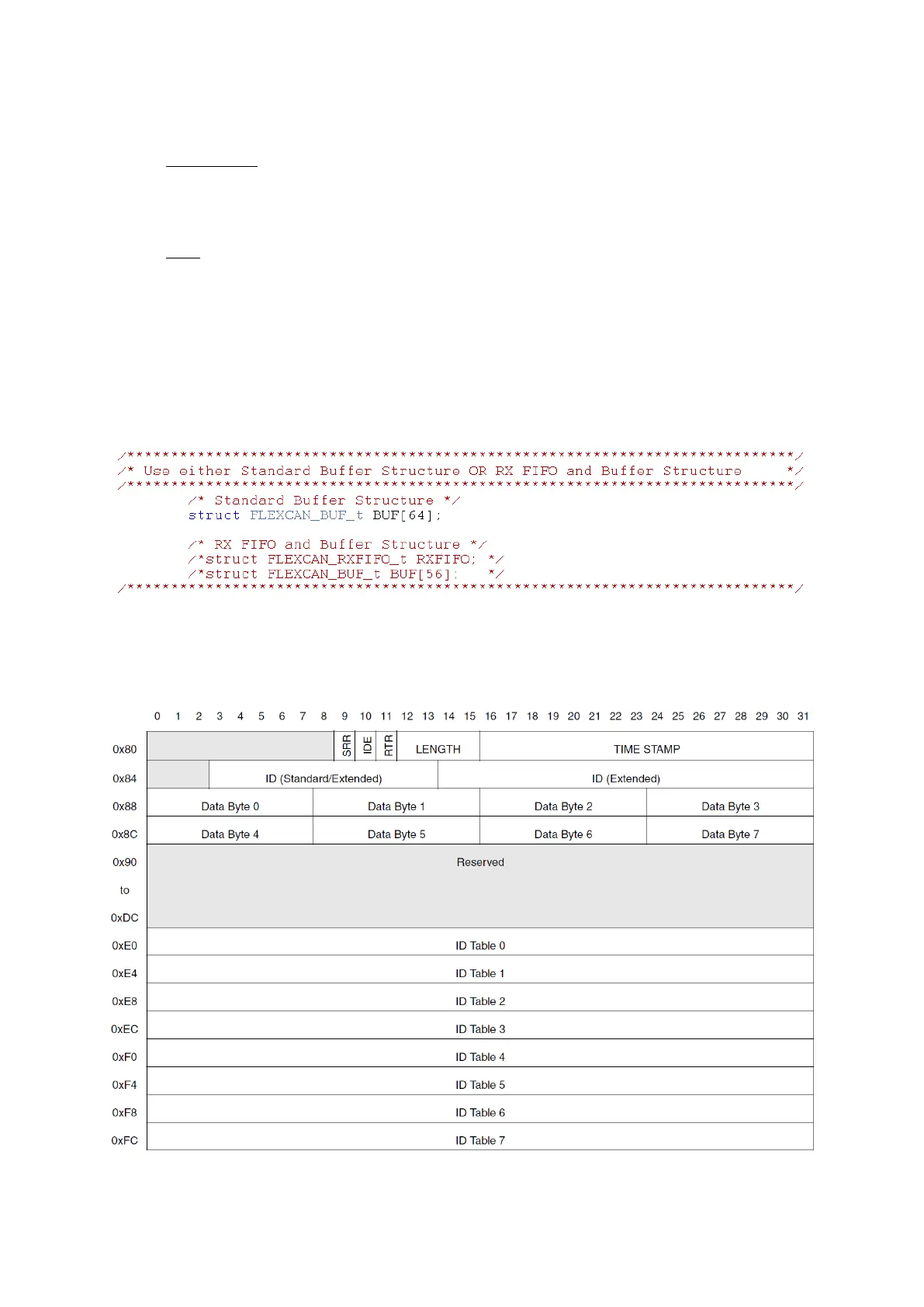

This engine is made of a single MB structure, with no code field, followed by 8 ID tables for

filtering the Rx frames.

Figure 121: Rx FIFO Structure (R.M. Rev8 – Fig. 22-3)

Loading...

Loading...