These fields are used to set the delay between the slave select signal and the start of the transfer.

PCSSCK: CS to SCK delay prescaler, used in establishing a delay between Chip Select

signal and the SCK start; the delay prescaler value is

=2×PCSSCK[0:1]+1.

Master mode only.

CSSCK : CS to SCK delay scaler, used in establishing a delay between Chip Select signal

and the SCK start; the delay scaler value is

= 2

[:]

. Master mode only.

=

×

/

These fields are used to set the once the transfer is finished and SCK is stopped.

PASC: after SCK delay prescaler, used in establishing a delay after the SCK stop; the delay

prescaler value is

=2×PASC[0:1]+1. Master mode only.

ASC : after SCK delay scaler, used in establishing a delay after the SCK stop; the delay

scaler value is

= 2

[:]

. Master mode only.

=

×

/

These fields are used to set the minimum CS idle time between two transfers. This delay is not

used in continuous transfer mode.

PDT: after transfer delay prescaler, used in establishing a delay between the end of one

conversion and the start of another one(the Chip Select signal) ; the delay prescaler

value is

=2×PDT[0:1]+1. Master mode only.

DT : after transfer delay scaler, used in establishing a delay between the end of one

conversion and the start of another one(the Chip Select signal) ; the delay scaler value is

= 2

[:]

. Master mode only.

=

×

/

Status and Interrupt Registers

The Transfer Count Register (TRC) counts the number of SPI transfers made. It has a 16-bit field

called SPI_TCNT. It automatically resets to 0 when it goes past 65535, or it can be forced to reset

using a command on transmit register.

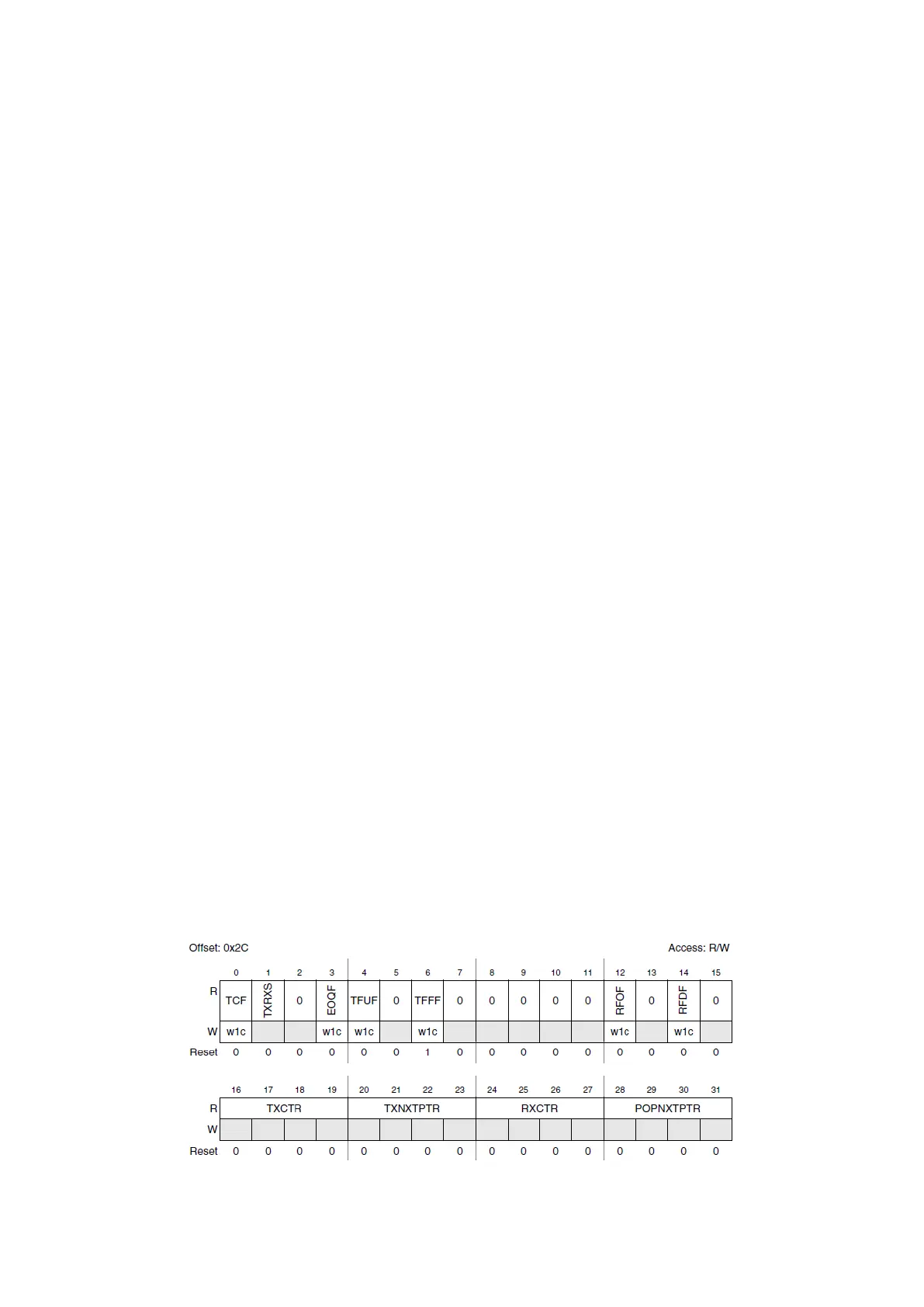

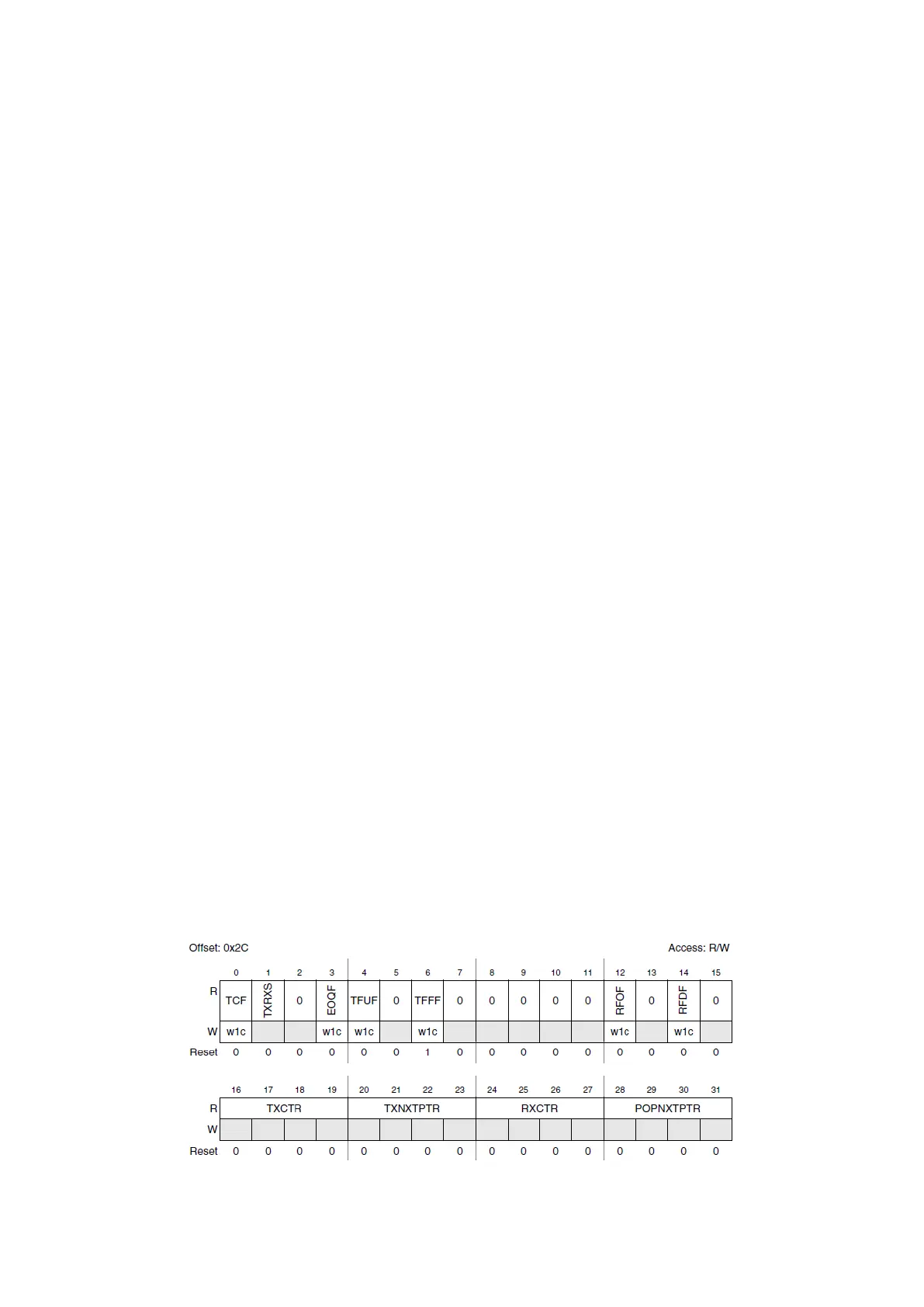

Figure 95 : DSPI Status Register (R.M. Rev8 –Fig. 23-6)

Loading...

Loading...