PSEG1: Phase Segment 1; this field defines the number of quanta in Phase Segment 1 as

PSEG1+1. Similarly for PSEG2 and PROPSEG.

BOFF_MSK is a mask for Bus Off interrupt. Set this bit for enabling the interrupt.

ERR_MSK is a mask for Error interrupt. Set this bit for enabling the interrupt.

CLK_SRC: Clock source select for FlexCAN peripheral clock. If set, the peripheral bus

clock is selected (usually FMPLL), else the FXOSC is selected.

LPB: Loop Back, if set, Loop Back mode is enabled. Rx input is ignored, and Tx output is

set to ‘1’, and FlexCAN perform self-test by treating its transmitted messages as received

(it acknowledges the message itself).

TWRN_MSK is a mask for Tx Warning interrupt. Set it for enabling the interrupt. (as well

as WRN_EN in MCR). Similarly for RWRN_MSK.

SMP: Sampling Mode, if set three samples are taken in a single bit-time and majority rule

is used. Otherwise only one sample determines the bit value.

TSYN: Timer Sync Mode, if set, when communication with multiple FlexCAN stations, a

special SYCN message is sent every time a message is received in MB0 (or MB8 if FIFO

enabled). This messages synchronises internal counters, therefore the increasing the

value of the timestamp.

LOM: Listen-Only mode, when set, FlexCAN will freeze all transmission operations and

error counters. It will not acknowledge messages but it will receive messages

acknowledged by other devices. Basically it is a sniffer.

There a register for accessing the internal free running counter: TIMER. It is mostly useful for

unlocking message buffers.

ID Filtering: There are two ways for ID filtering for received frames, the selection is made with

BCC bit in MCR:

Legacy masks: There is a global Rx Mask (RXGMASK), this 32 bit register mask IDs of all

MBs and FIFOs frames. If the corresponding bit is set, then that bit of the ID will be

compared, else it will be accepted without checking. There are also two specific masks,

Rx 14 Mask (RX14MASK) for MB14 (and element 6 of FIFO ID Filter Table) and Rx 15

Mask (RX15MASK) for MB15 (and element 7 of FIFO ID Filter Table).

Individual masks: there are 64 separate 32-bit masks for each MB: RXIMR0 to RXIMR63.

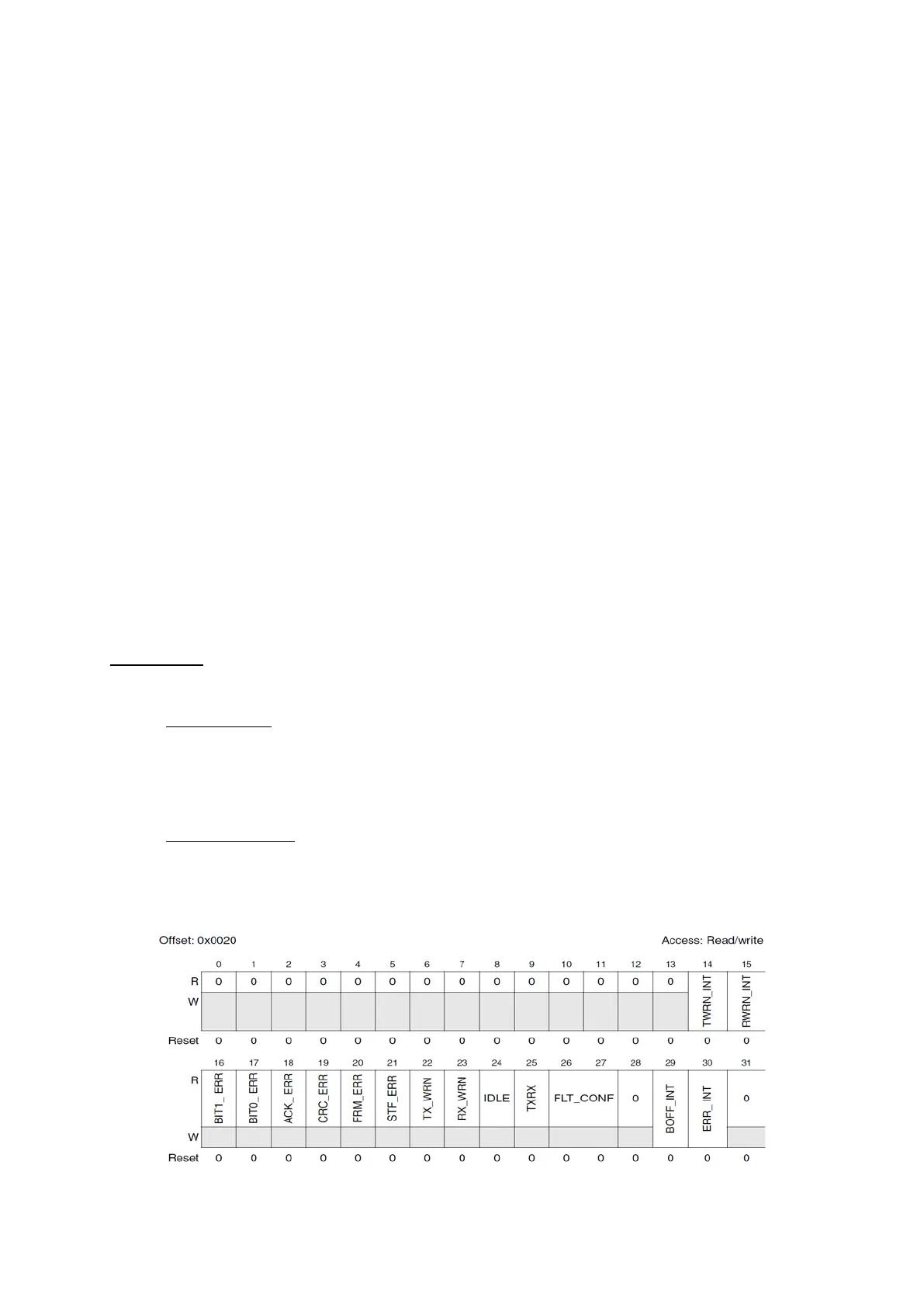

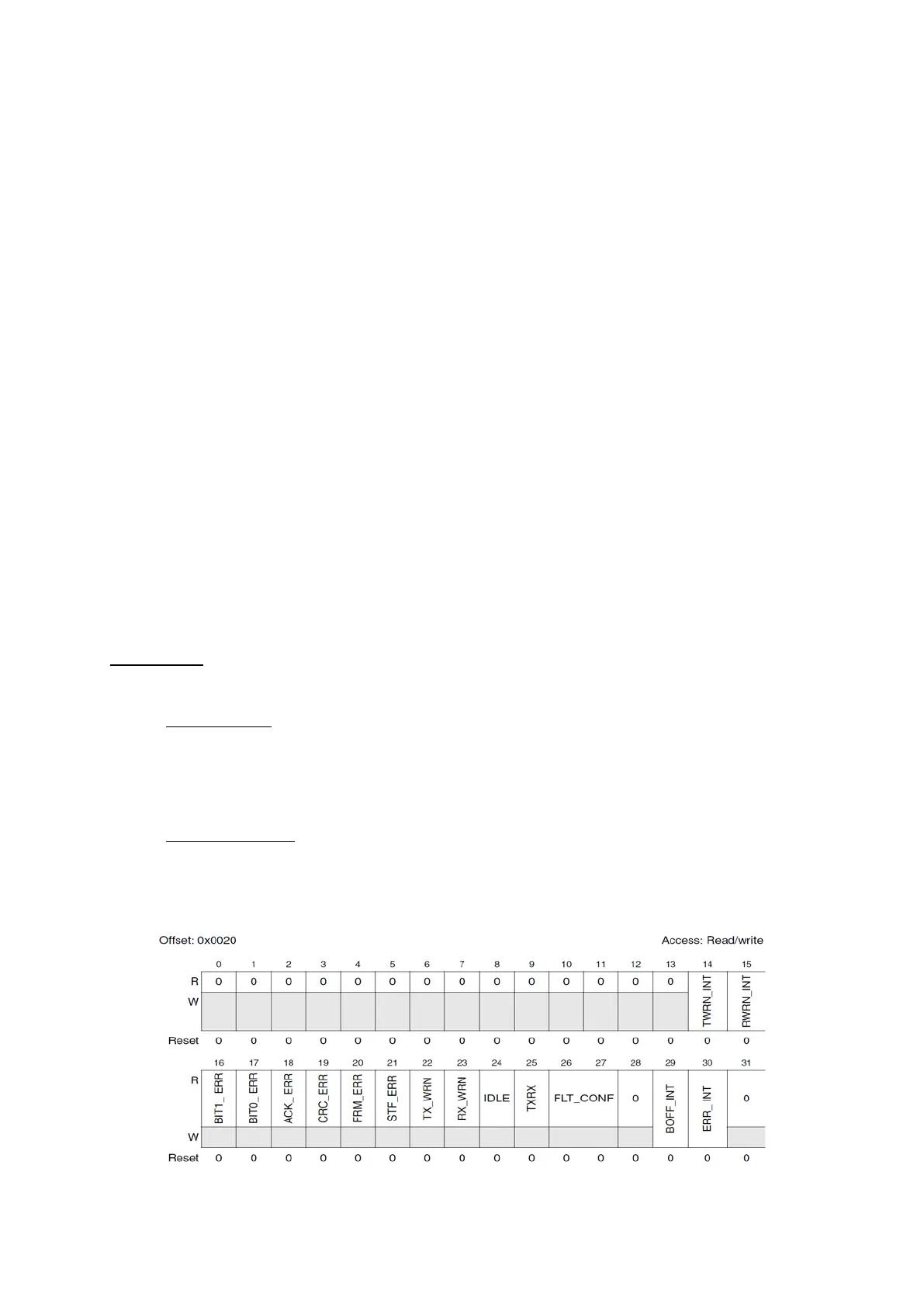

Status and Interrupt Registers

The Error and Status Register (ESR) is an important register for interrupt and error flags.

Figure 125: Error and Status Register

Loading...

Loading...