HALT: if FRZ is set, the module enters into Freeze Mode. Message buffers and registers

are accessible but no reception or transmission can be done. FlexCAN leaves Freeze

Mode is this bit or FRZ bit is cleared.

NOT_RDY: read only; if set, then the module is in Disable or Freeze mode; else, it is in

Normal, Listen-Only or Loop-Back mode.

FRZ_ACK: read only; indicates if the module is in Freeze Mode.

LPM_ACK: read only; indicates if the module is in Disable Mode.

WRN_EN: when this bit is set, error counter warning TWRN_INT and RWRN_INT flags in

the status register are set if respective error counters go over 96.

SRX_DIS: if this bit is cleared, then FlexCAN module receives whatever it sends (but in

never stores it in any MB, even if the IDs match, and no interrupts are generated on

reception).

BCC: Selection between legacy masks (0) and individual masks (1) for ID filtering. (see

below).

LPRIO_EN: enables local priority for Tx MB arbitration, by adding 3 more address bits

(not transmitted). (see Message Buffer paragraph).

AEN: Abort enable, if set, TX_ABORT code can be used in message buffers.

IDAM(ID Acceptance Mode): allows selecting between different ID Table modes for the

RX FIFO engine (A=00, B=01, C=10, D=11).

MAXMB: maximum number of message buffers, number of MB used in matching and

arbitration is MAXMB+1. (Maximum 64 in MB mode, 56 in RX FIFO mode).

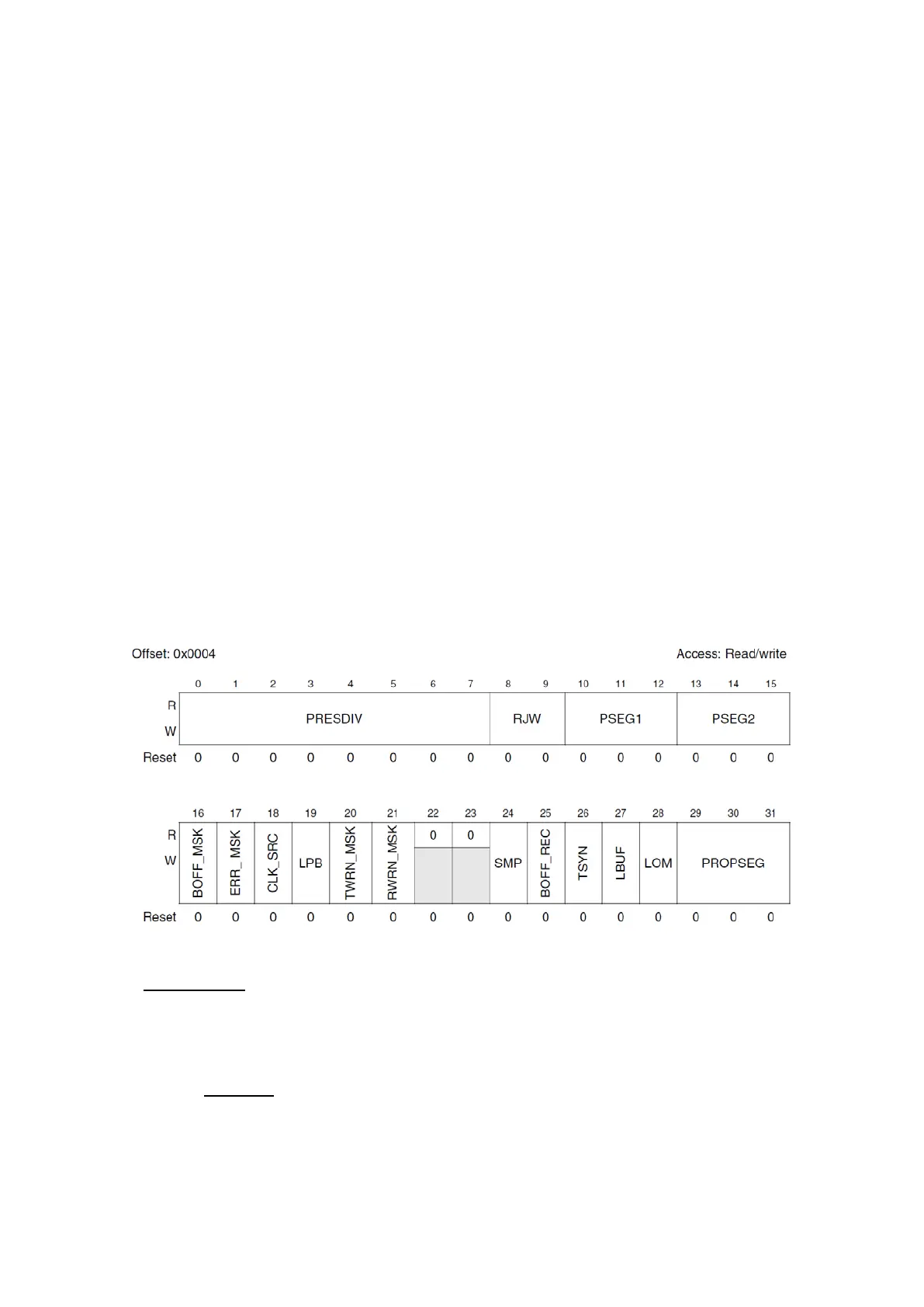

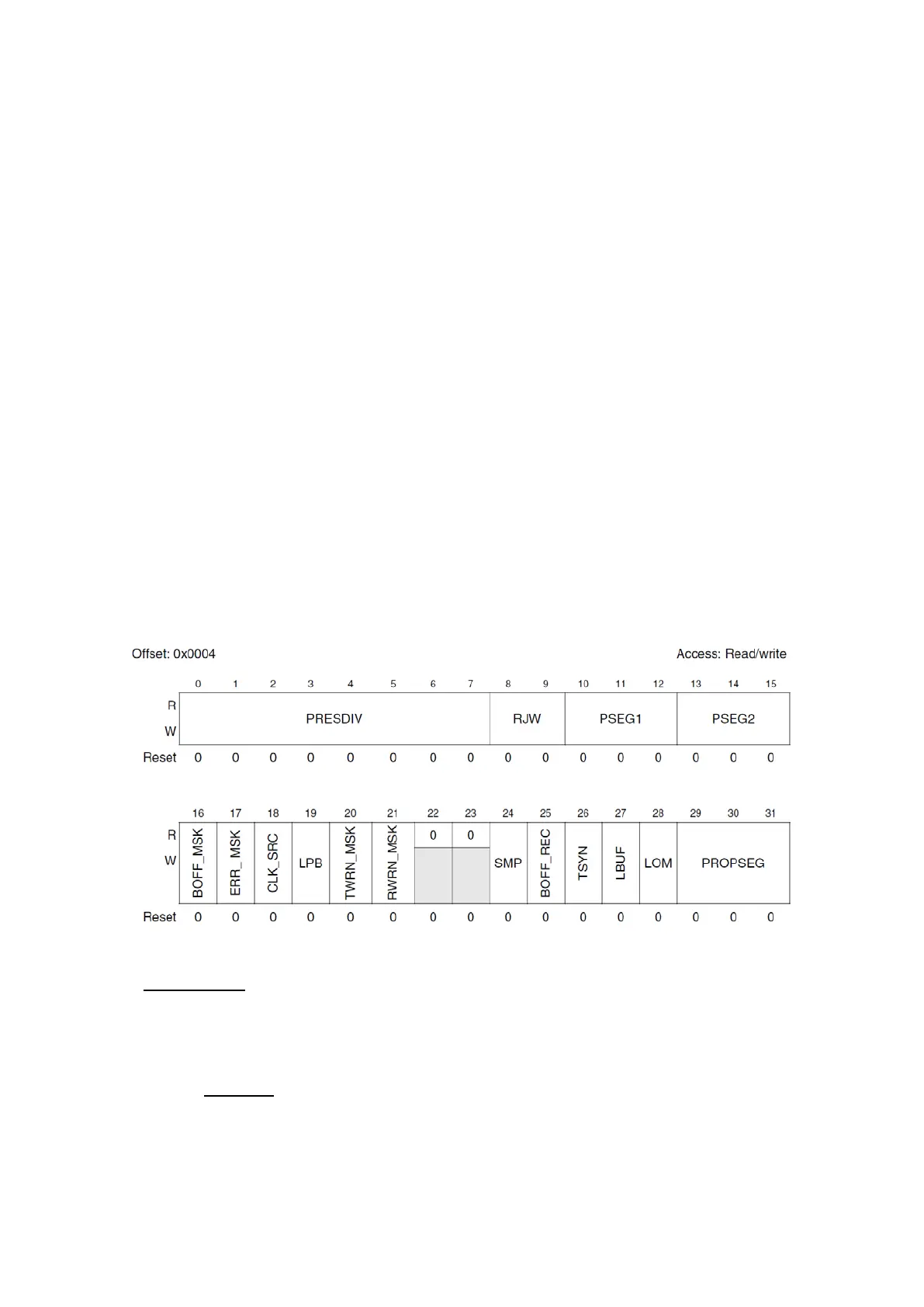

Figure 124: Control Register (R.M. Rev8 – Fig. 22-6)

The CTRL register is another important register, especially for configuring bit rate. Important

fields are:

PRESDIV: Prescaler Division Factor, this prescaler is used for setting the FlexCAN serial

clock from the FlexCAN peripheral clock, defining the time quantum in the protocol.

=

.

RJW: Resync Jump Width; The number of quanta in Resynchronisation Jump Width is

RJW+1.

Loading...

Loading...