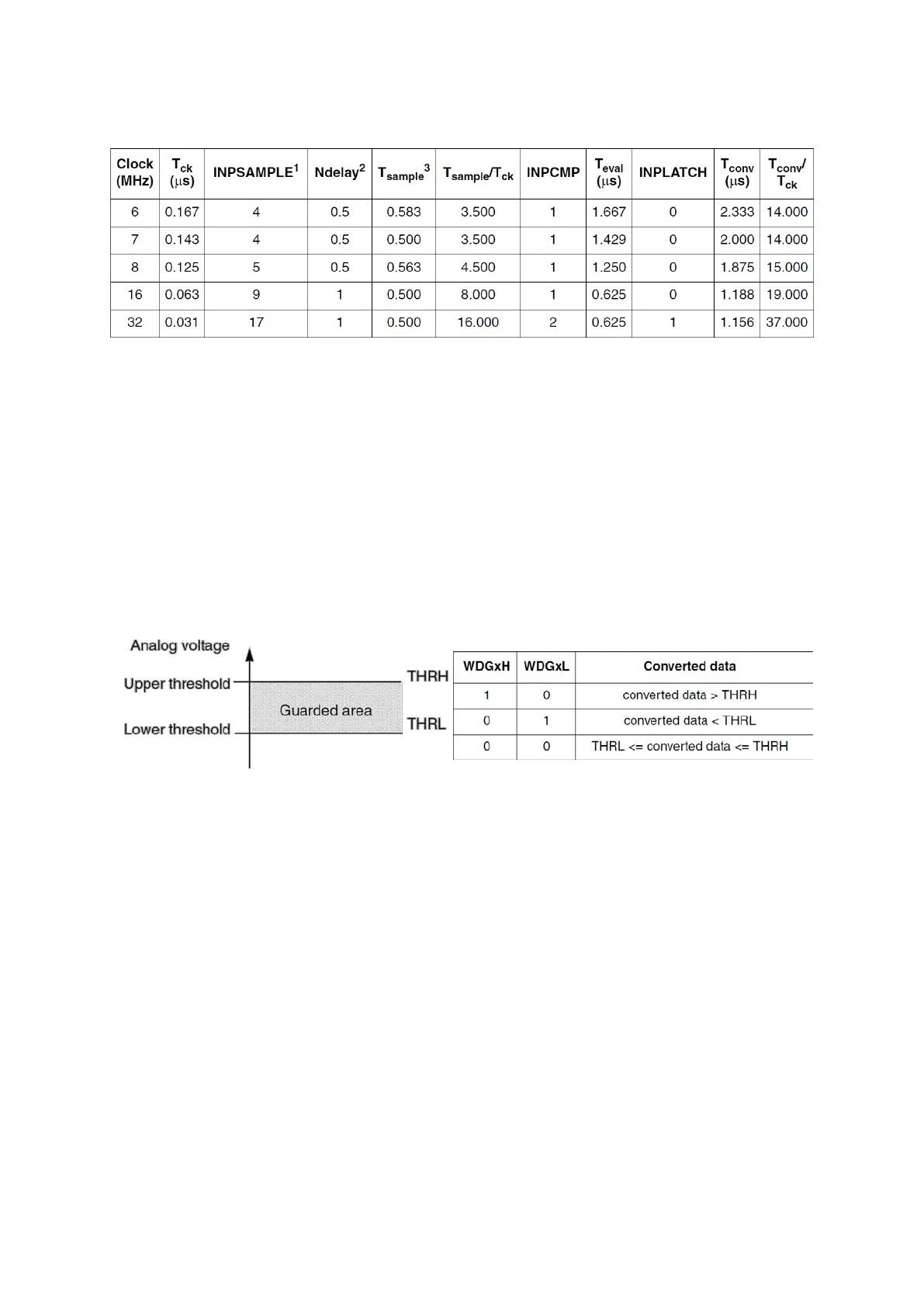

The following table gives some example values for different clock settings:

Figure 69 : ADC sampling and conversion timing (R.M. Rev8 – Table 25-2)

1.4.

For higher quality sampling, resetting the sampling capacitor after a previous sampling is

needed; the ADC capacitor is charged or discharged to one of the two internal voltage references.

This phase can be enabled for a channel, and it would take as much time as a sampling phase. It

is also possible to bypass the real sampling phase to get a conversion of the reference value.

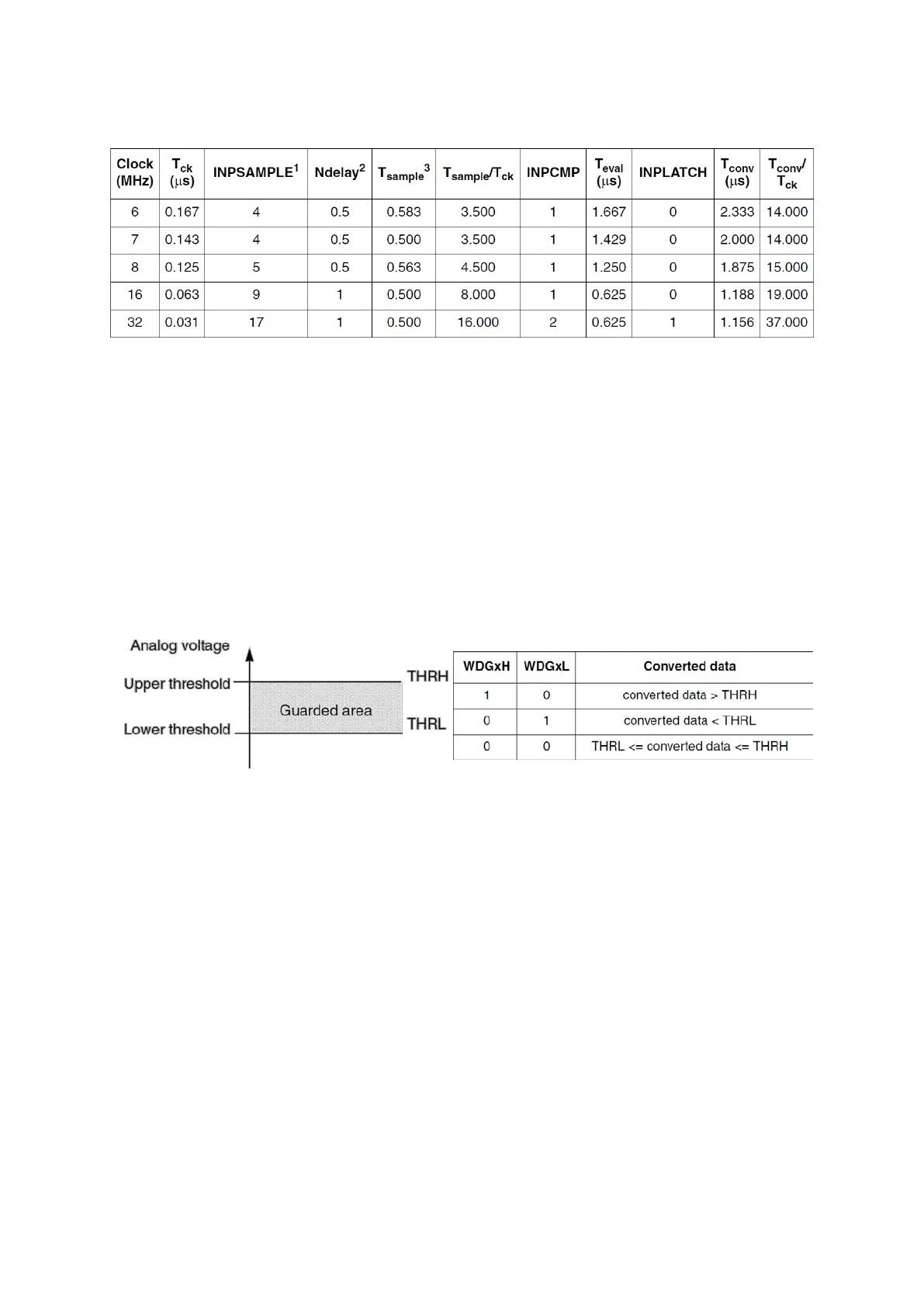

There are four analog watchdogs in this module, and each of them can monitor a channel

conversion to check if it lies in a guarded area limited by a lower and an upper threshold.

Figure 70 : Analog Watchdog (R.M. Rev8 – Fig. 25-7/Table 25-5)

In the watchdog status register, two bits called WDGxH and WDGxL whether there has been a

threshold violation or not. An interrupt can be generated at a lower and/or higher threshold

violation.

Low power consumption modes

The ADC module is by default in power-down mode and this state has to be exited before

starting conversions. The software can request this mode by using the appropriate bit field and

once the ongoing conversion if over, ADC will go into this mode. The ADC’s status can be checked

using the status register. If the CTU is enabled, ADC cannot go to the power-down mode; the

conversion has to end for that.

Another power saving mode is the auto-clock-off mode, where the ADC module automatically

turns off its clock when there is no pending conversion.

Loading...

Loading...