The MB zone of the FIFO is used for accessing frames. The engine automatically changes data

read on MB depending on FIFO’s state. Reading data is similar to the MB structure, first the

Control & Status word is read, then the ID field and the Data.

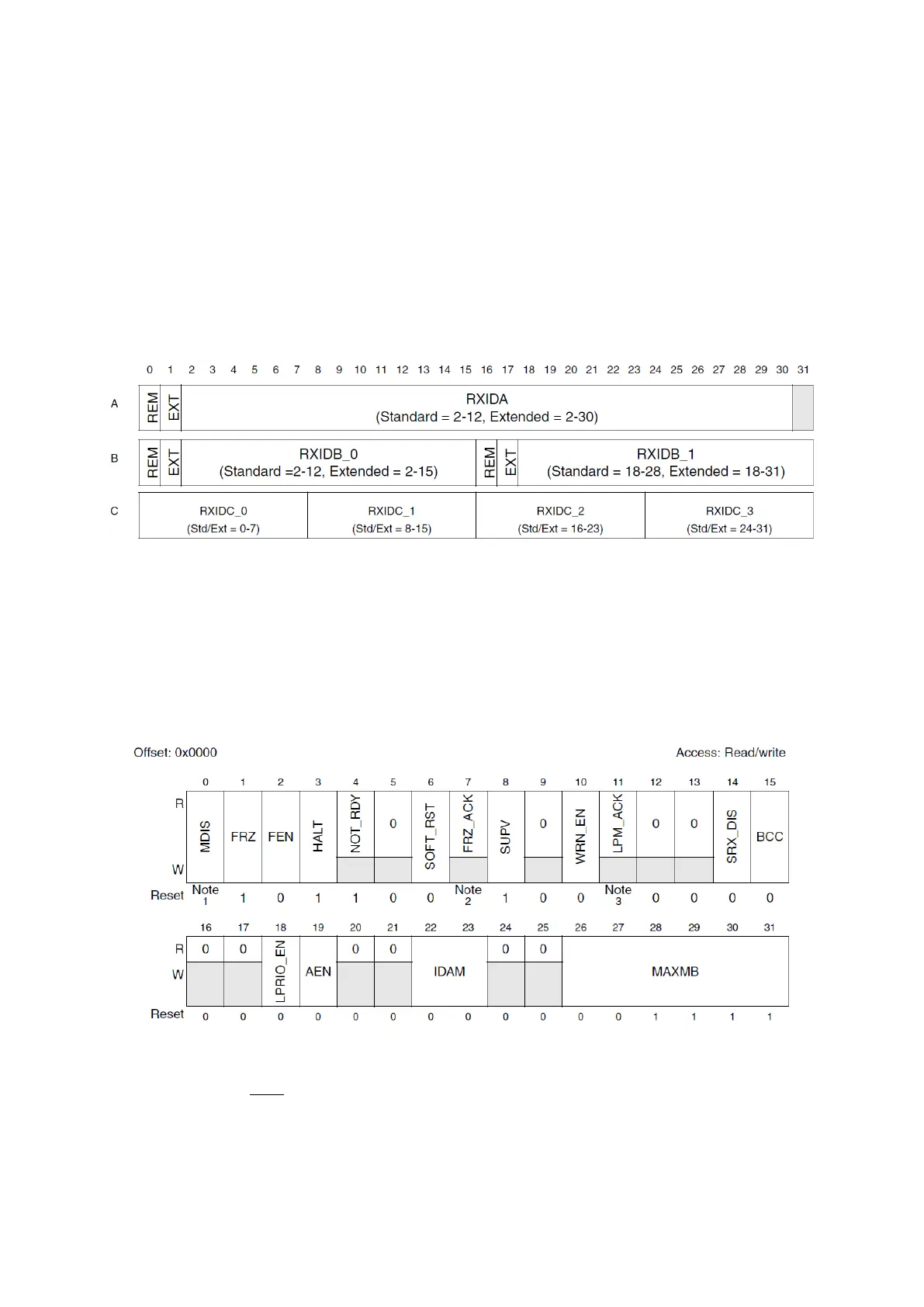

The 8 words of the ID table can be used in four separate modes configurable in MCR register:

A. Up to 8 standard/extended ID acceptance criteria,

B. Up to 16 standard ID acceptance criteria (or 16 extended ID acceptance criteria only

over 14 most significant bits),

C. Up to 32 ID acceptance criteria over the 8 most significant bits of the ID,

D. All frames rejected.

Figure 122: Fields of the ID Table words depending on the selected ID mode (R.M. Rev8 – Fig. 22-4)

The figure above shows the different fields in an ID Table depending on its mode. When REM

(Remote Frame) is set, remote frames can be accepted and data frames are rejected (it’s the

opposite when REM is cleared).

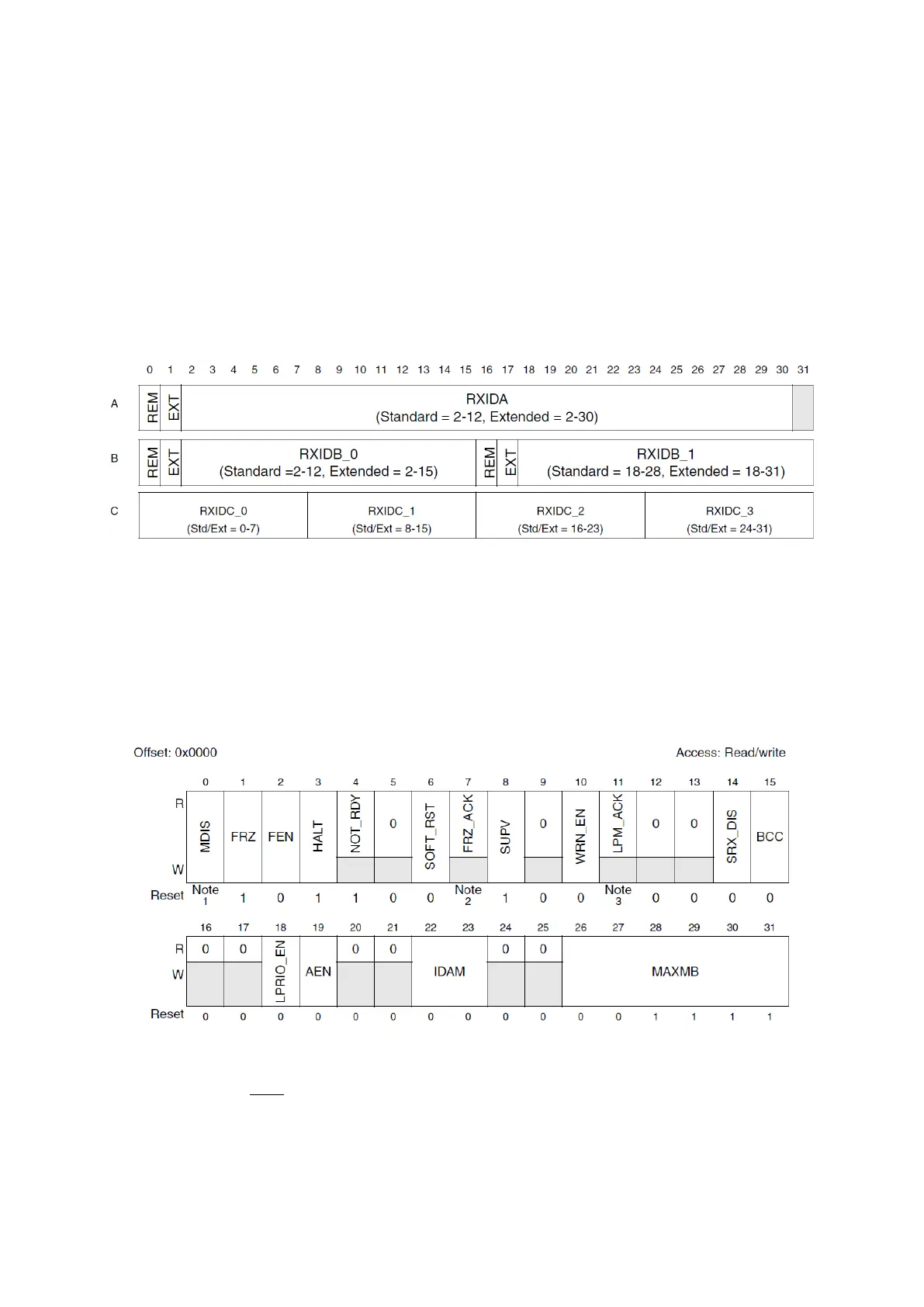

For configuring FlexCAN, following registers can be used.

Figure 123: Module Configuration Register (R.M. Rev8 – Fig. 22-5)

Important fields of MCR are:

MDIS (Module Disable): this bit has to be cleared to enable FlexCAN.

FRZ (Freeze): if set, this module is enabled to enter Freeze Mode.

FEN (FIOF Enable): if set, the Rx FIFO is enabled, replacing MB[0…7],

Loading...

Loading...