Once the conversion starts, JSTART is reset for further conversion requests. At the end of each

conversion JEOX interrupt is issued and at the end of an injected sequence, JECH interrupt is

triggered.

Any ongoing conversion can be stopped using the ABORT bit in the configuration register, then

the next channel in line will be converted. Using ABOTCHAIN all pending channel conversions

can be aborted. If the last channel of a sequence is aborted, then ECH interrupt is raised.

ADC clock and conversion timing

This module’s clock frequency can be set to the peripheral set 3’s clock frequency or to its half.

When the half divider is not used, it is recommended to not use a divider for the peripheral

clock, as it may not give a 50% duty cycle clock.

The conversion timing can be more or less configured, and each type of channel type can have a

particular timing setting. Conversion time consists of a sampling phase, a latching phase and an

evaluation phase.

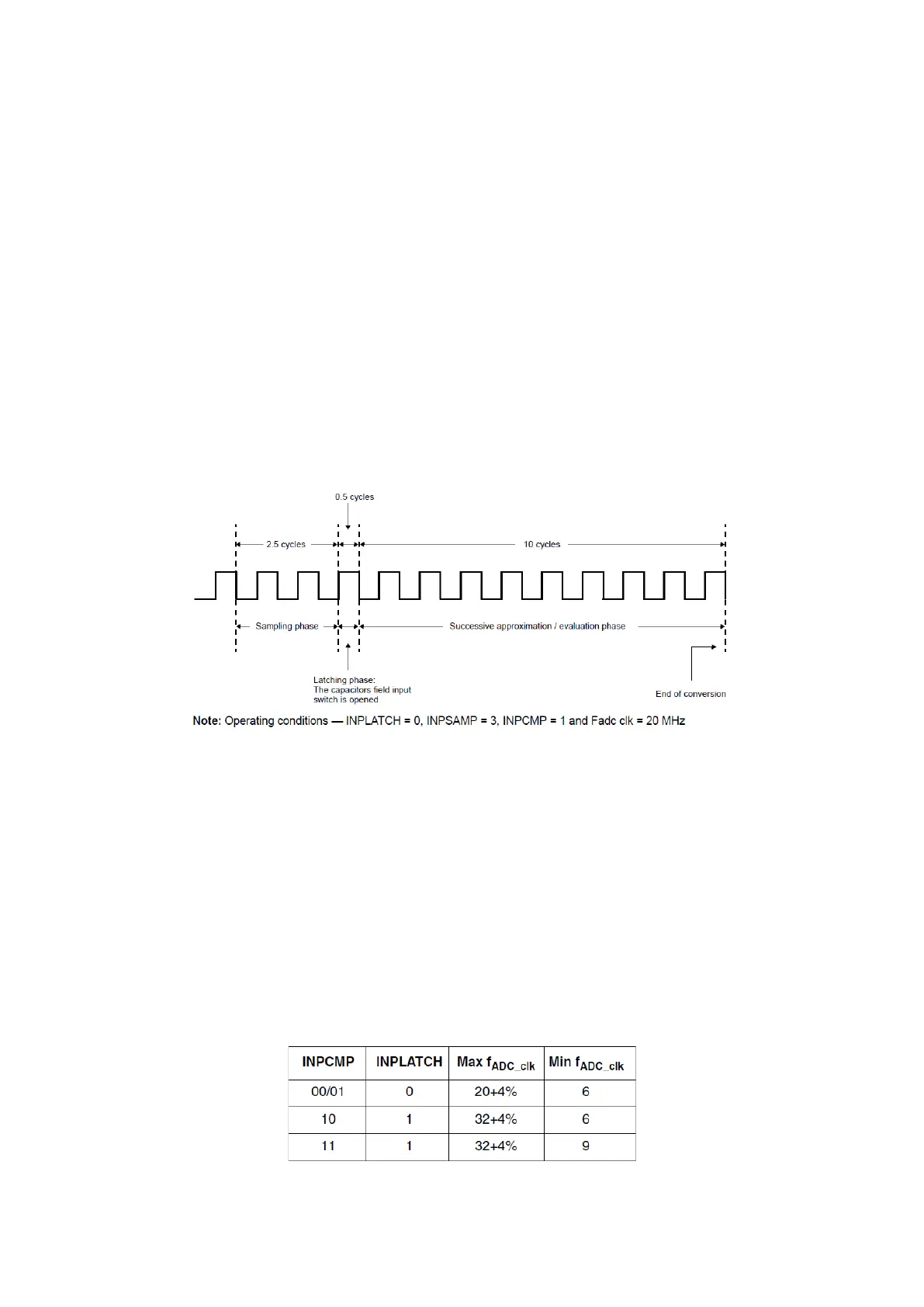

Figure 67 : Sampling and conversion timing example (R.M. Rev8 – Fig. 25-4)

The sampling phase is when the ADC’s internal sampling capacitor is connected to the input pin

and charges up to the input voltage value. This phase’s duration is defined as

= INPSAMP

, where INPSAMP is configurable, and has to be greater than

or equal to 3,

is 0.5 if INPSAMP6 and 1 otherwise. And

has to be greater than or

equal to 500ns.

is the ADC’s clock, derived from the peripheral clock.

The latching phase is when the capacitor’s switch is opened and its duration is

.

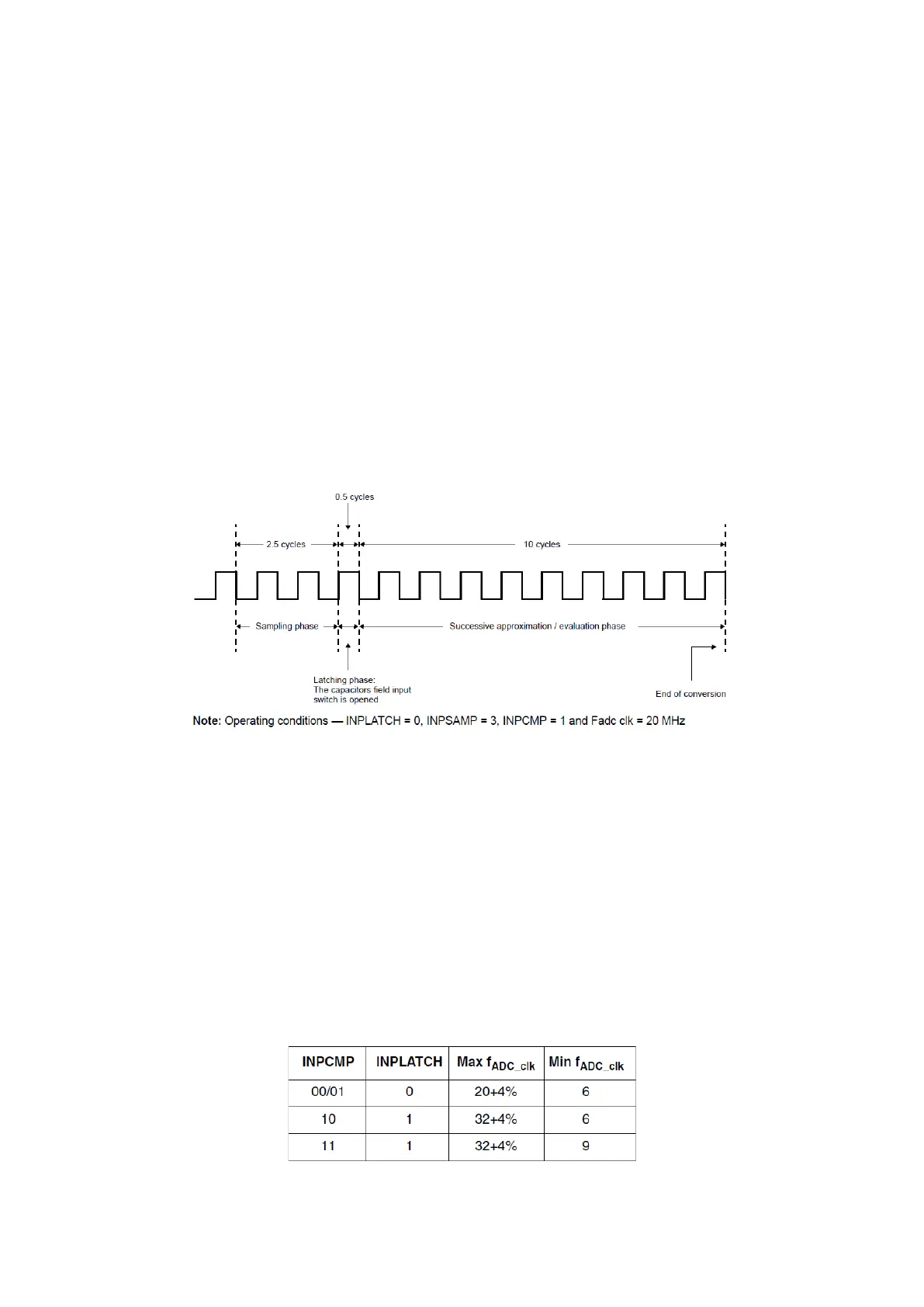

The evaluation phase is the time needed for successive approximation to be performed, its

duration is

= 10 INPCMP

, where INPCMP1 and INPLATCH < INPCMP. These two

values are configurable, and have to be set using the following table.

Figure 68 : Max/min ADC_clk related to parameters (R.M. Rev8 – Table 25-3)

Loading...

Loading...