registers should not be changed while DSPI is running. Most of its fields are only used in the

master mode.

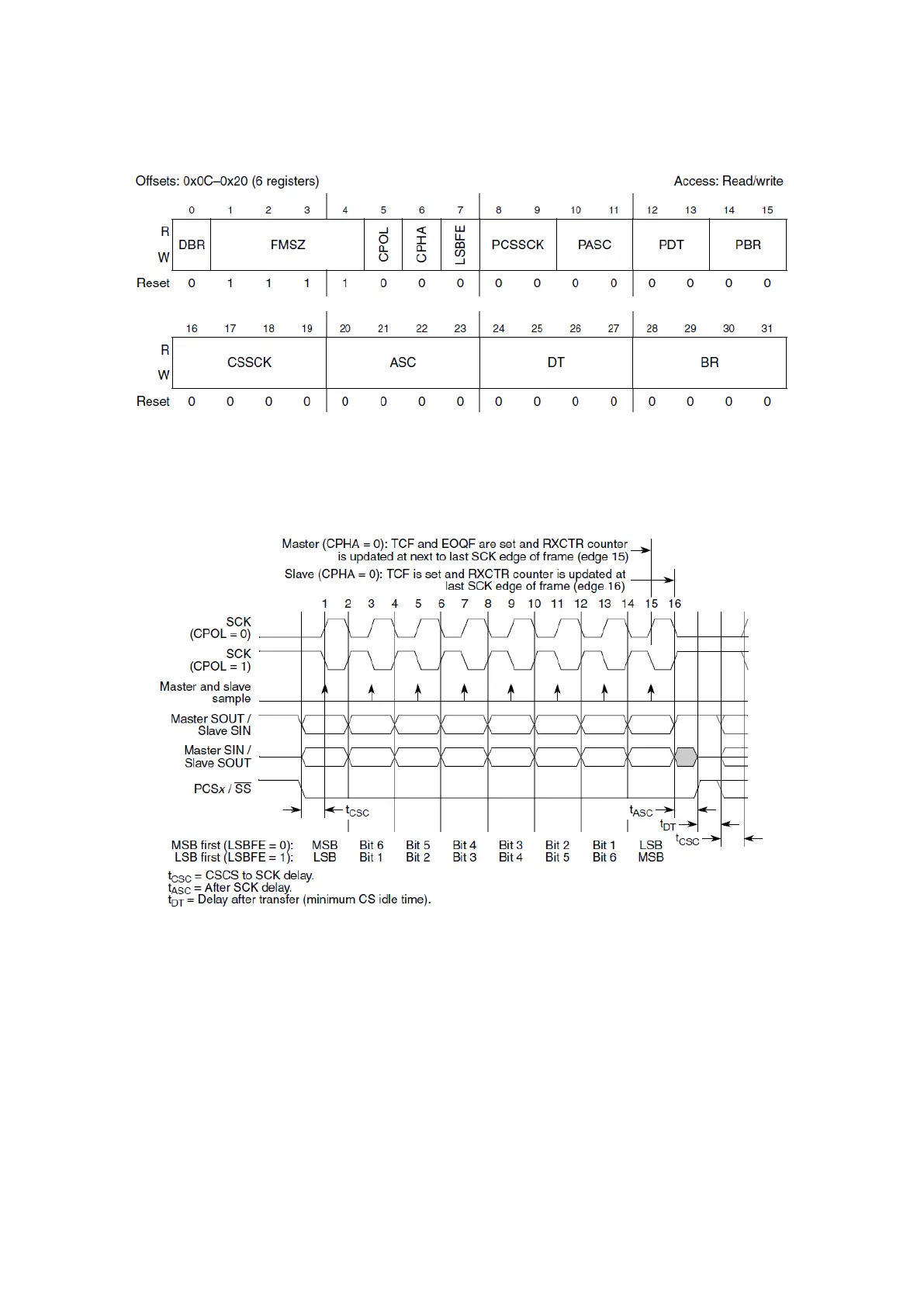

Figure 92 : Clock and Transfer Attributes Registers (CTAR) (R.M. Rev8 –Fig. 23-5)

This configuration register’s fields are explained in different subsections below for better clarity.

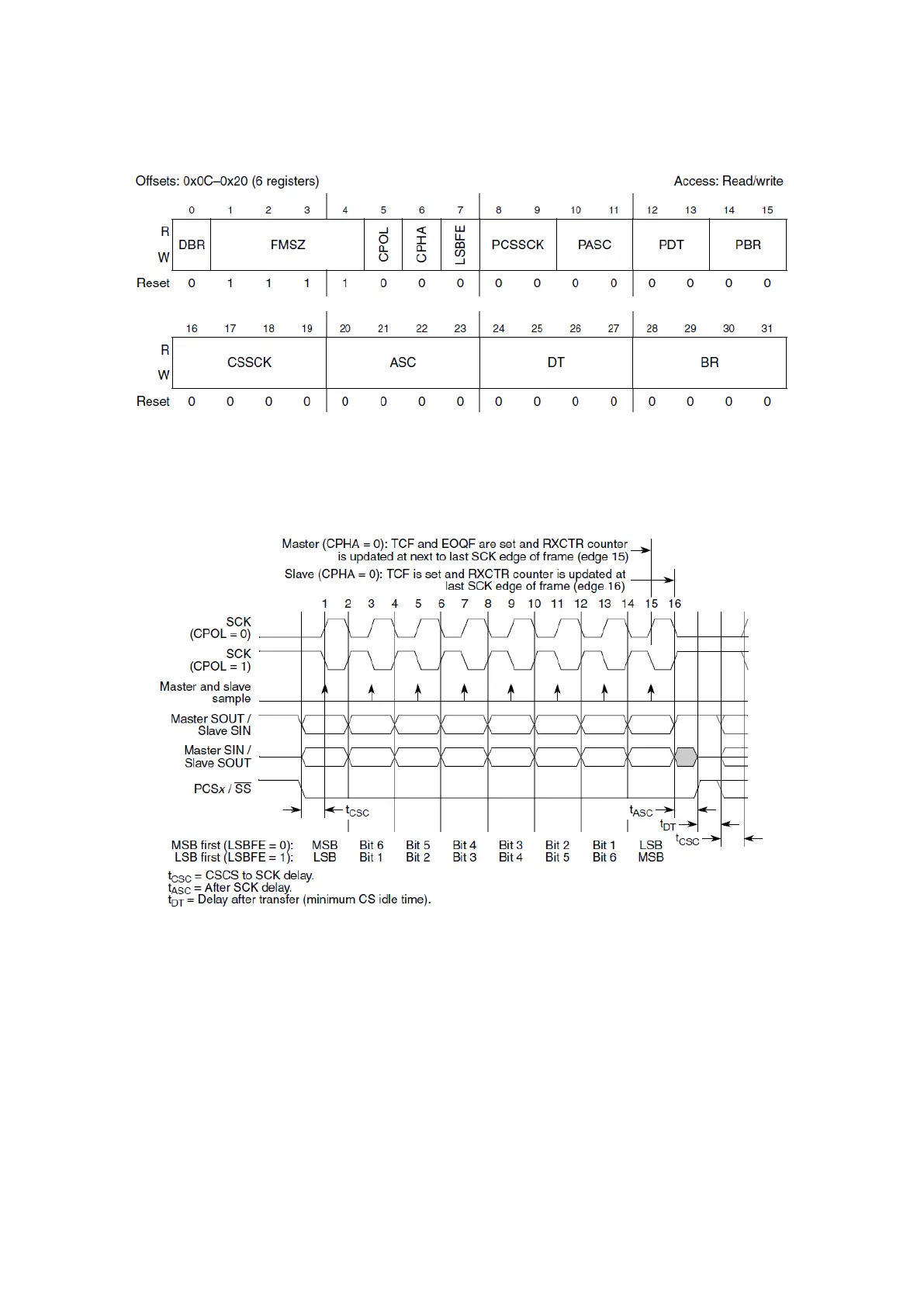

The figure below illustrates the influence of different parameters on the transfer.

Figure 93 : Illustration of flag timings on classic SPI transfer format (R.M. Rev8 –Fig. 23-16)

2.3.1.

These attributes are used to select the parameters related to the transferred data like its size, its

order, on which edge it is read or changed.

FMSZ: frame size, selects the number of bits transferred per frame. Both master and

slave modes need this. The frame size value is FMSE+1 (has to be between 4 and 16).

CPOL: clock polarity, if cleared, the inactive value of SCK is low, else it is high. Both

master and slave modes need this.

CPHA: clock phase, if cleared, the data is captured on the leading edge of SCK, otherwise

it is captured on the falling edge. Both master and slave modes need this.

Loading...

Loading...