Appendix D: POST Code Diagnostic LED Decoder Intel® Server Board S5500BC TPS

Intel order number: E42249-009 Revision 1.8

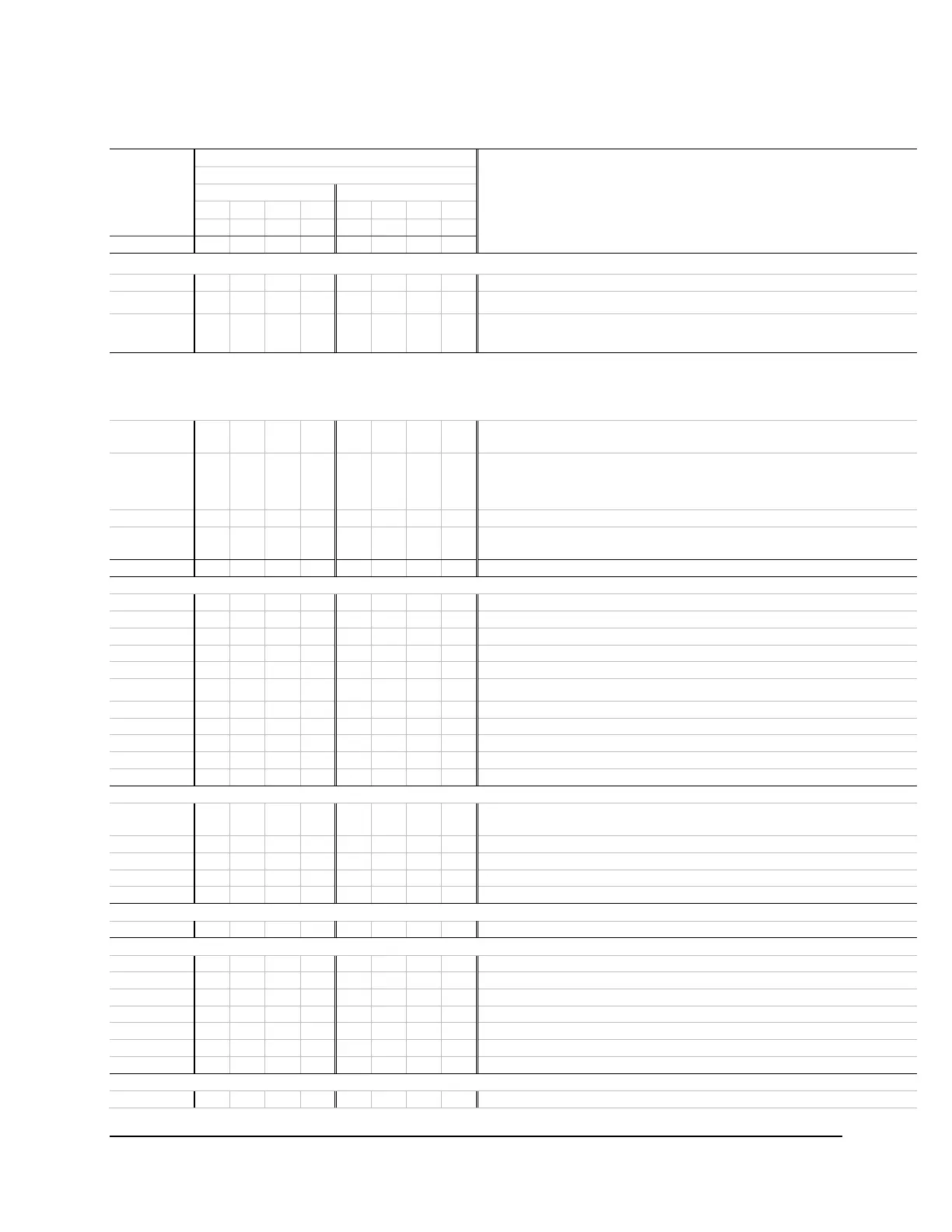

Table 81. Diagnostic LED POST Code Decoder

Multi-use code – This POST Code is used in different contexts.

Seen at the start of Memory Reference Code (MRC)

Start of the very early platform initialization code

Very late in POST, it is the signal that the operating system has

switched to virtual memory mode

Memory Error Codes (Accompanied by a beep code)

Note that these are codes used in early POST by Memory Reference Code. Later in POST these same codes are used for

other Progress Codes. (These progress codes are not controlled by BIOS and are subject to change at the discretion of

the Memory Reference Code team.)

No Usable Memory Error: No memory in the system, or SPD bad so

no memory could be detected

Channel Training Error: DQ/DQS training failed on a channel during

memory channel initialization. If no usable memory remains, system

is halted.

Memory Test Error: memory failed Hardware BIST.

Population Error: RDIMMs and UDIMMs cannot be mixed in the

system

Mismatch Error: more than 2 Quad Ranked DIMMS in a channel.

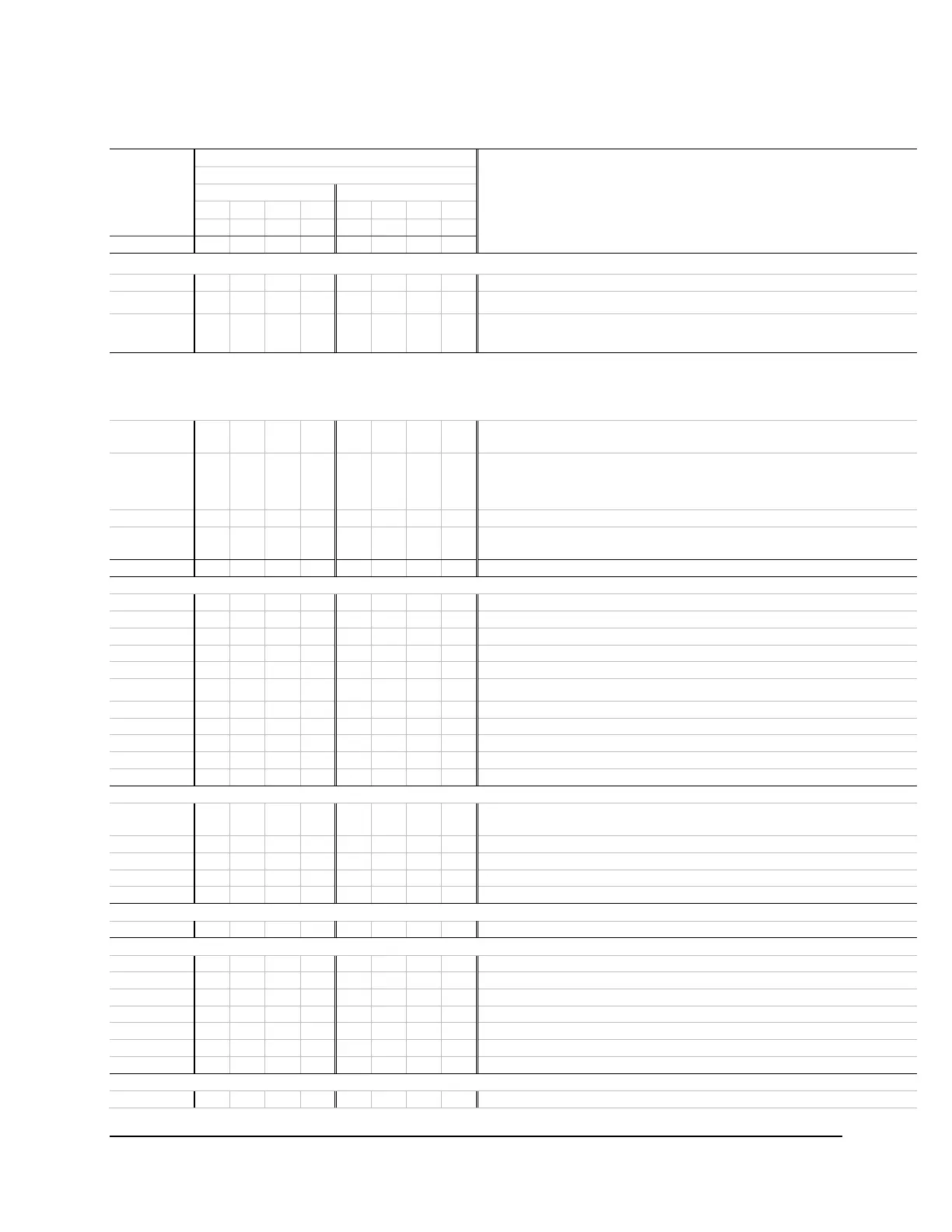

Memory Reference Code Progress Codes (Not accompanied by a beep code)

Chipset Initialization Phase

Clock Initialization Phase

SPD Data Collection Phase

Memory Map Creation Phase

Early processor initialization (flat32.asm) where system BSP is

selected

Power-on initialization of the host processor (bootstrap processor)

Host processor cache initialization (including AP)

Starting application processor initialization

Initializing a chipset component

Reading configuration data from memory (SPD on DIMM)

Detecting presence of memory

Programming timing parameters in the memory controller

Configuring memory parameters in the memory controller

Optimizing memory controller settings

Initializing memory, such as ECC init

Loading...

Loading...