Functional Architecture Intel

®

Server Board S5500BC TPS

Intel order number: E42249-009 Revision 1.8

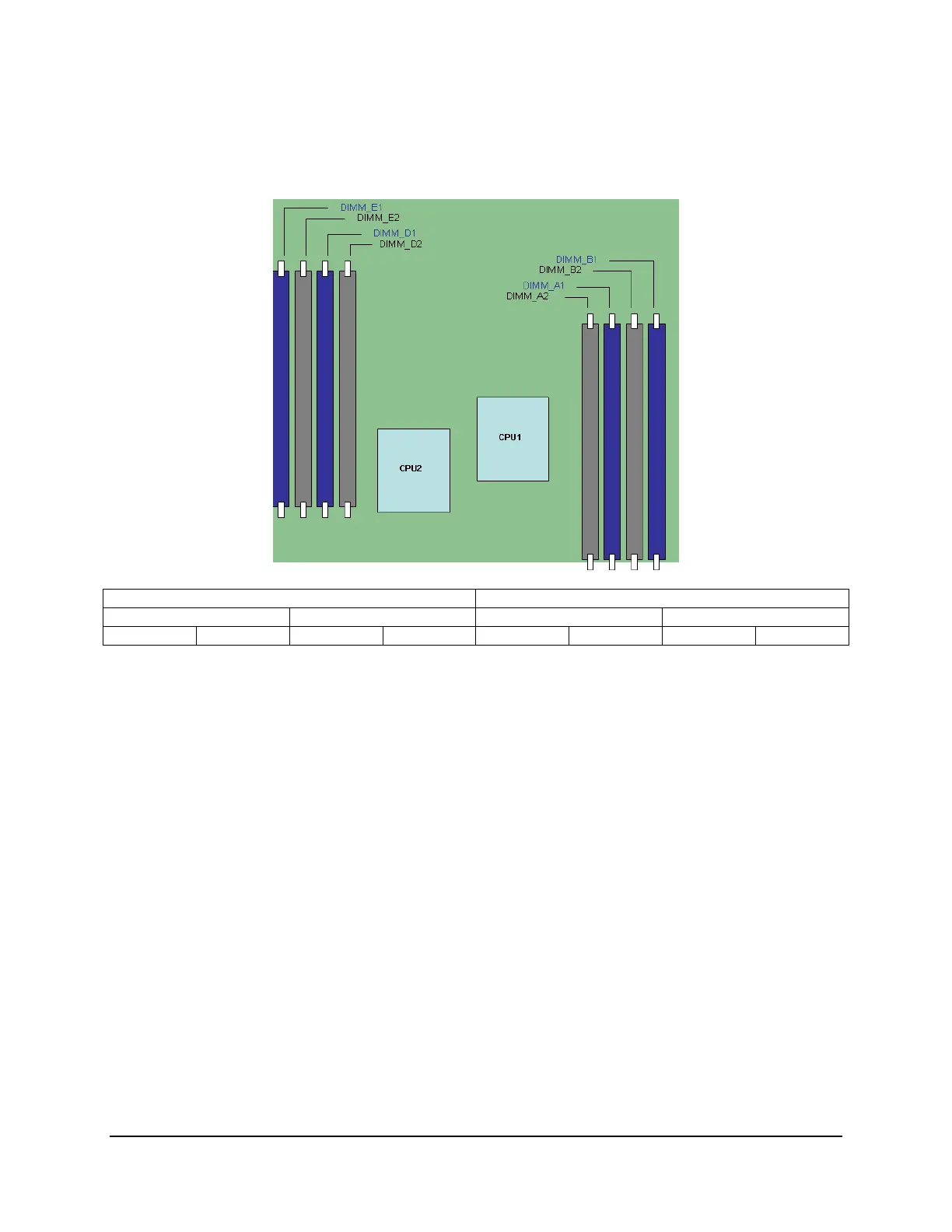

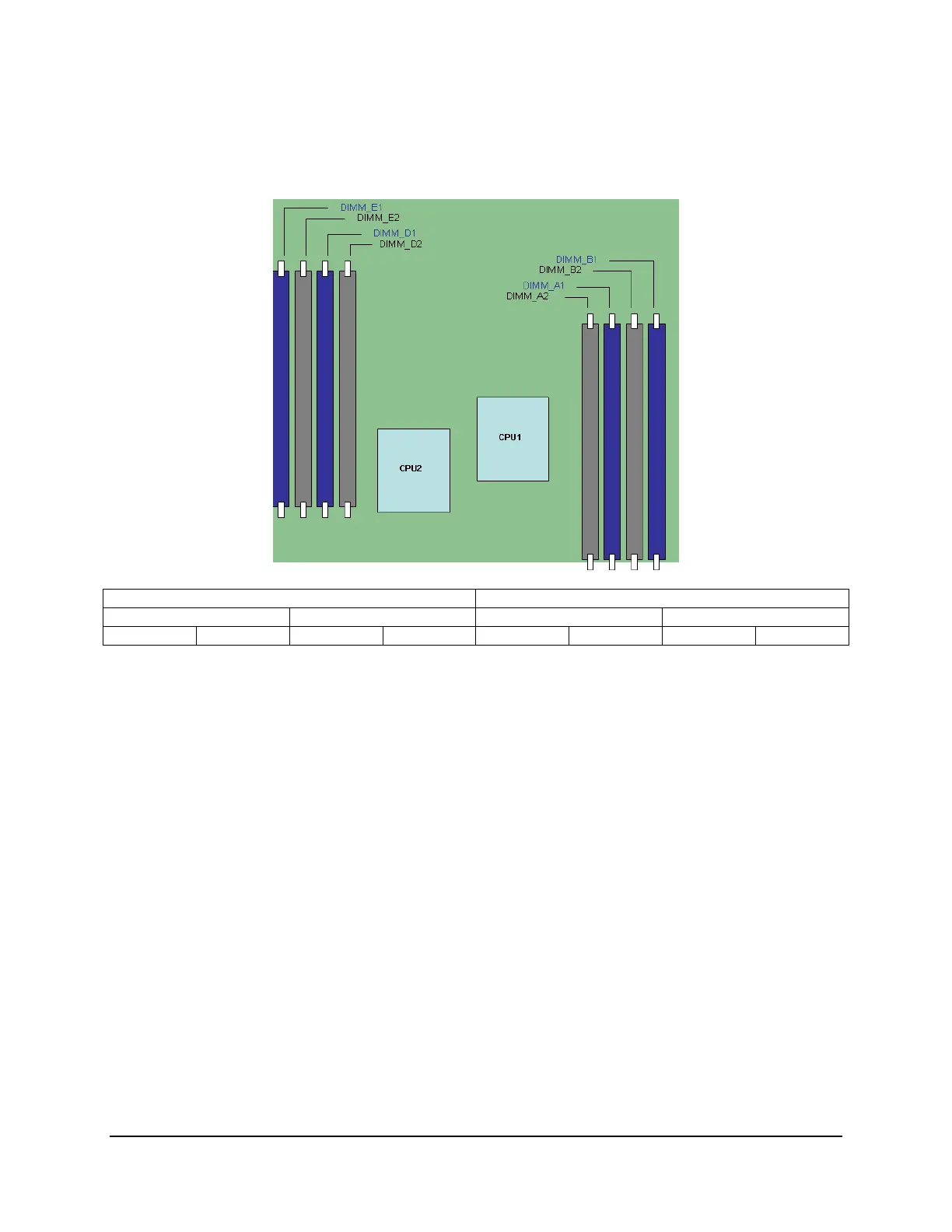

3.2.2 DIMM Population Requirements

DIMMs on this board are organized into physical slots on the DDR3 memory channels divided

between two processor sockets. For more information, refer to the following figure.

Figure 15. DIMM Organization

DIMMs are organized into physical slots on DDR3 memory channels that belong to the

processor sockets.

The memory channels for processor socket 1 are identified as channels A and B. The

memory channels for processor socket 2 are identified as channels D and E.

Each node supports four DIMM sockets (two DIMM sockets per channel).

The DIMM identifiers on the silkscreen on the board provide information about which

channel and therefore which node they belong to. For example, DIMM_A1 is the first slot

on channel A of node 1. DIMM_D1 is the first DIMM socket on channel D of node 2.

You must populate the memory slots for each DDR3 channel from the Intel

®

Xeon

®

5500

processor series and 5600 series on a farthest first fashion. This also holds true for

Independent Channel mode. Therefore, you cannot populate/use DIMM_A2 if DIMM_A1

is empty.

When CPU socket 1 is empty, any DIMM memory in channel A and B is unavailable.

When CPU socket 2 is empty, any DIMM memory in channel D and E is unavailable.

If channel A and channel B are empty, CPU socket 1 can still function if memory is

available from channel D and channel E. However, platform performance will suffer

latency due to remote memory.

Loading...

Loading...