Intel

®

Server Board S5500BC TPS Functional Architecture

Revision 1.8 Intel order number: E42249-009 19

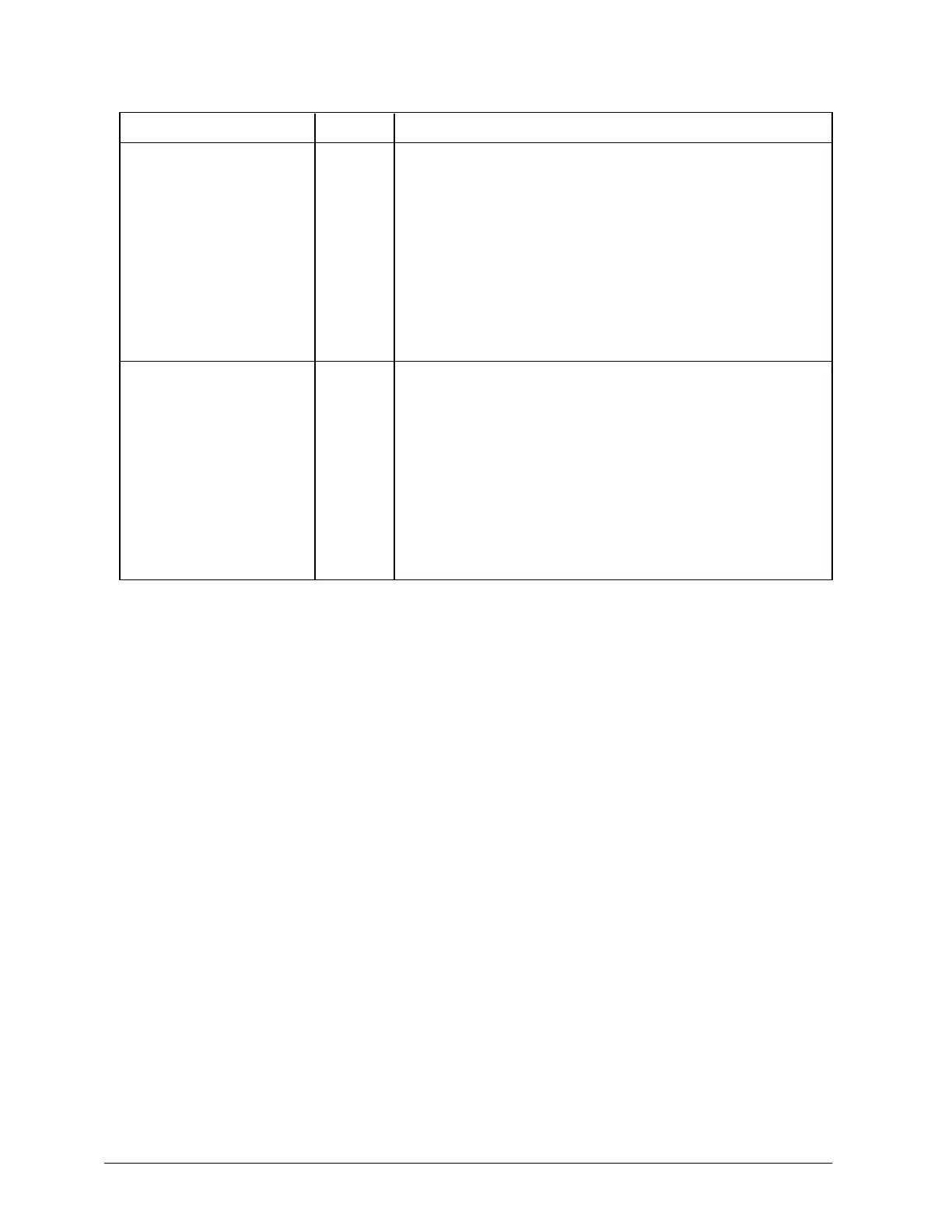

Processor microcode

missing

The BIOS detects the error condition and responds as

follows:

1. Logs the error into the SEL.

2. Alerts the BMC of the configuration error with an

IPMI command.

3. Does not disable the processor.

4. Displays “816x: Processor 0x unable to apply

microcode update” message in the error manager.

5. Pauses the system for user intervention.

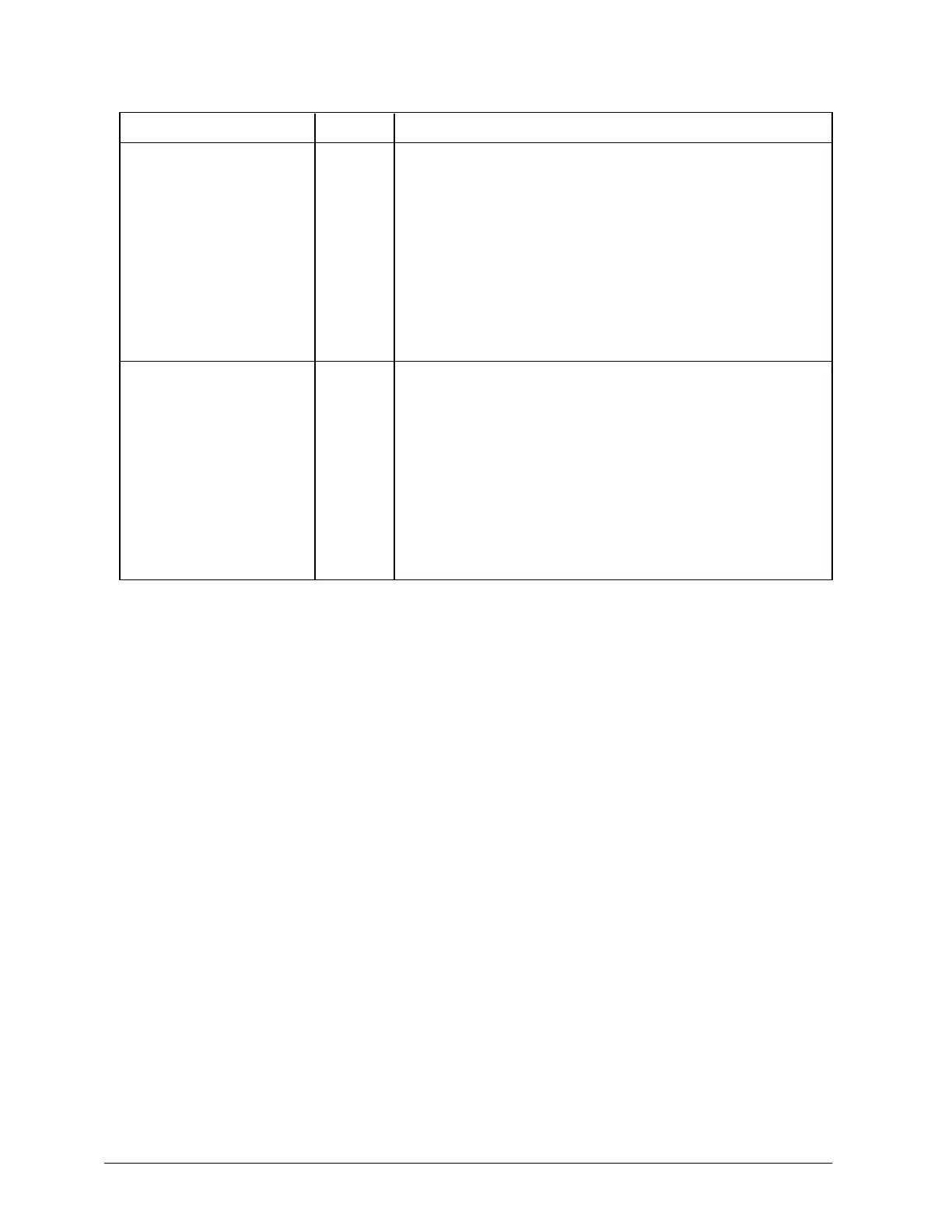

Processor Intel

®

QuickPath Interconnect

speeds not identical

The BIOS detects the error condition and responds as

follows:

1. Logs the error into the system event log (SEL).

2. Alerts the BMC of the configuration error with an

IPMI command.

3. Does not disable processor.

4. Displays “0195: Processor Front Side Bus speed

mismatch detected” message in the error manager.

5. Halts the system.

3.1.3 Multiple Processor Initialization

Intel

®

IA-32 processors have a microcode-based bootstrap processor (BSP) arbitration protocol.

The BSP starts executing from the reset vector (F000:FFF0h). A processor that does not

perform the role of BSP is referred to as an application processor (AP).

The Intel

®

Server Board S5500BC is a dual-socket server platform based on Intel

®

QuickPath

Interconnect replacing Front Side Bus architecture. At reset, one BSP per processor socket is

selected. However, the BIOS POST Power On Self Test (POST) code requires only one

processor for execution. This requires the BIOS to elect a single system BSP using registers in

the chipset. The BIOS cannot guarantee which processor will be the system BSP, only that a

system BSP is selected. In the remainder of this document, system BSP is referred to as BSP.

The BSP is responsible for executing the BIOS POST and preparing the server to boot the

operating system. At boot time, the server is in virtual wire mode and the BSP alone is

programmed to accept local interrupts (INTR driven by programmable interrupt controller (PIC)

and non-maskable interrupt (NMI)).

As a part of the boot process, the BSP wakes each AP. When awakened, an AP programs its

memory type range registers (MTRRs) to be identical to those of the BSP. All APs execute a

halt instruction with their local interrupts disabled. If the BSP determines an AP exists is a lower-

featured processor or has a lower value returned by the CPUID function, the BSP switches to

the lowest-featured processor in the server. The system management mode (SMM) handler

expects all processors to respond to an SMI.

Loading...

Loading...