Functional Architecture Intel

®

Server Board S5500BC TPS

Intel order number: E42249-009 Revision 1.8

The rules for determining the operating frequency of the memory channels are simple, but not

necessarily straightforward. There are several limiting factors, including the number of DIMMs

on a channel and organization of the DIMM (single-SR, double-DR, or quad-rank-QR):

800, 1066, or 1333 MHz is the maximum speed

possible.

The speed of the slowest component the slowest DIMM or the IMC determines the

maximum frequency, subject to further limitations.

A single 1333 MHz DIMM (SR or DR) on a channel may run at full 1333 MHz speed.

If two SR/DR DIMMs are installed on a channel, the speed is limited to 1066 MHZ.

A single QR RDIMM on a channel is limited to 1066 MHz.

In addition, rules in the following table also determine the global common memory system

frequency.

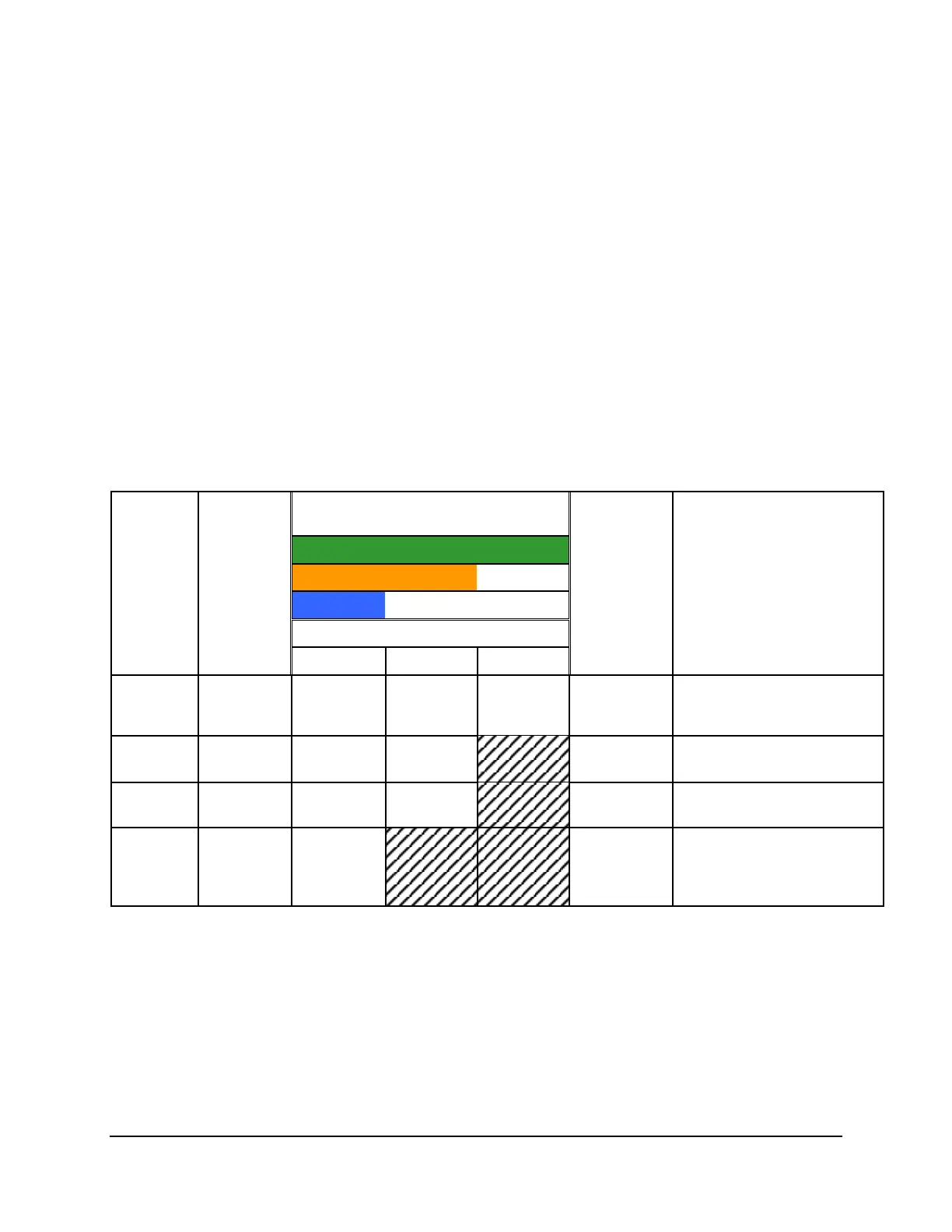

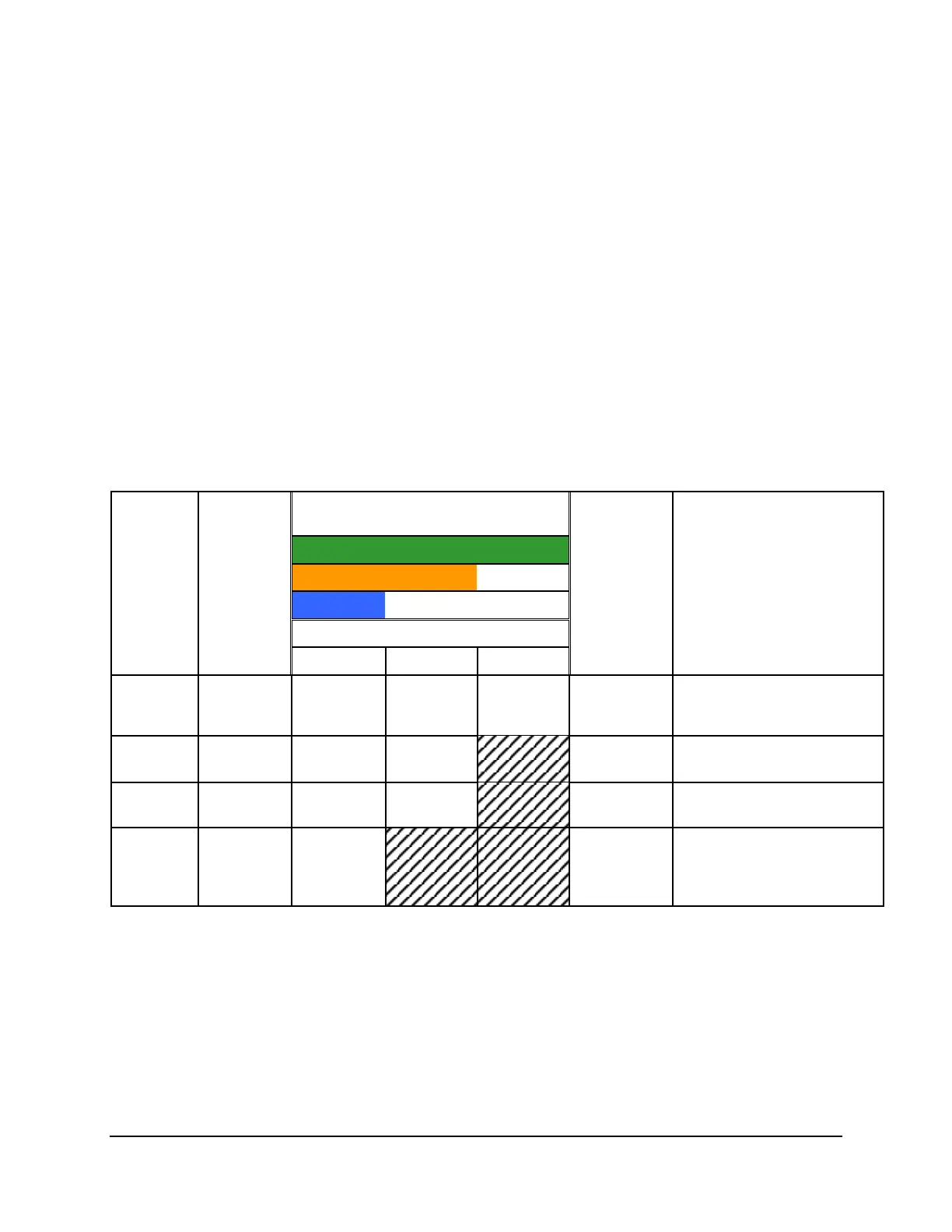

Table 8. Memory Operating Frequency Determination for Intel® processor 5500 series

DIMM

Populated

per Channel

IMC Frequency of Installed Processors

(1333MHz, 1066MHz, or 800MHz)

Ranks Per

DIMM

SR: Single-

Rank

DR: Dual-

Rank;

QR: Quad-

Rank

Memory Running Frequency (Y/N)

1 DPC (SR/DR) runs at fastest

common frequency of DIMMs

and processor IMCs

1 QR RDIMM runs at 1066MHz

maximum

2 DPC (SR/DR) run at

1066MHz maximum

When a QR RDIMM is on a

channel with any other

RDIMM, maximum frequency

is 800MHz

Loading...

Loading...