Functional Architecture Intel

®

Server Board S5500BC TPS

Intel order number: E42249-009 Revision 1.8

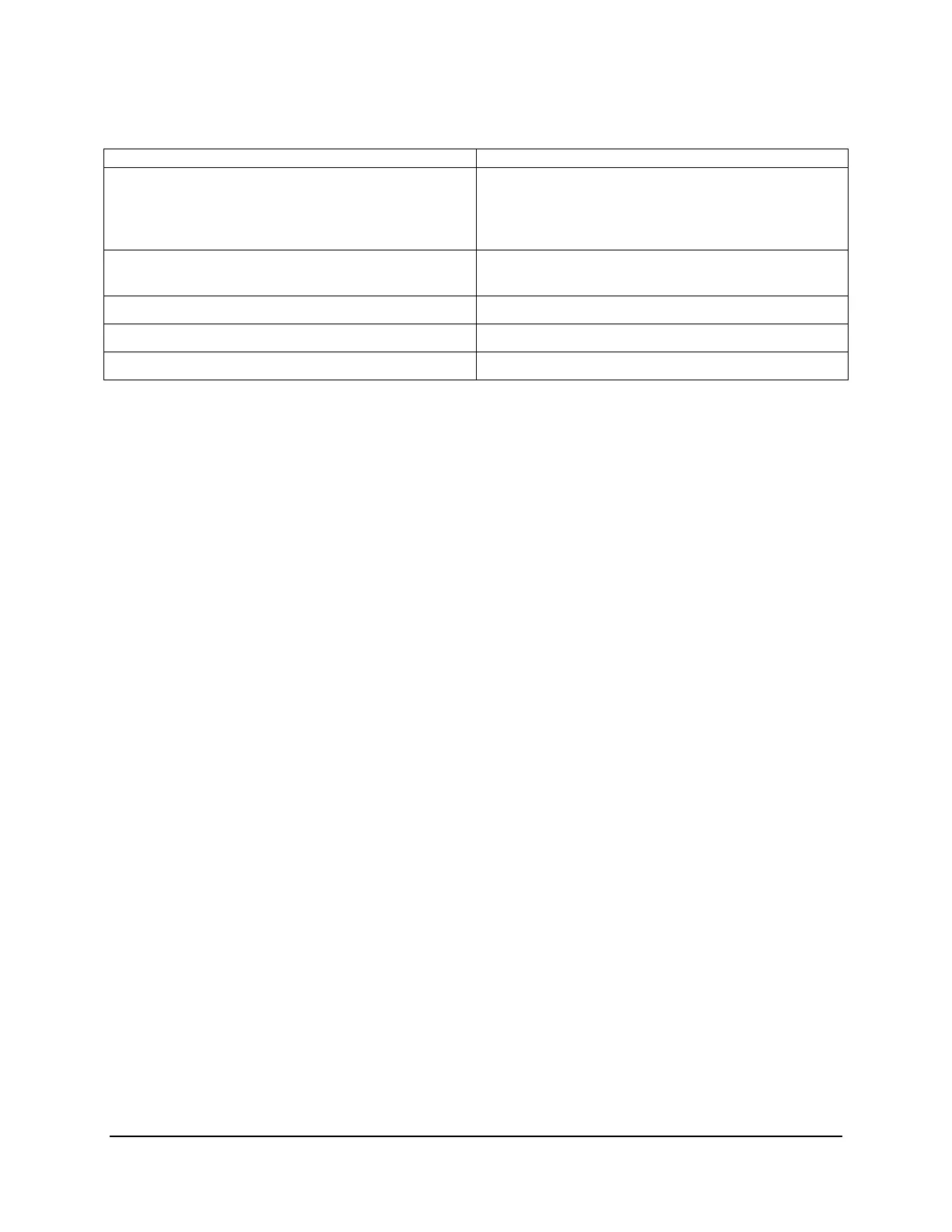

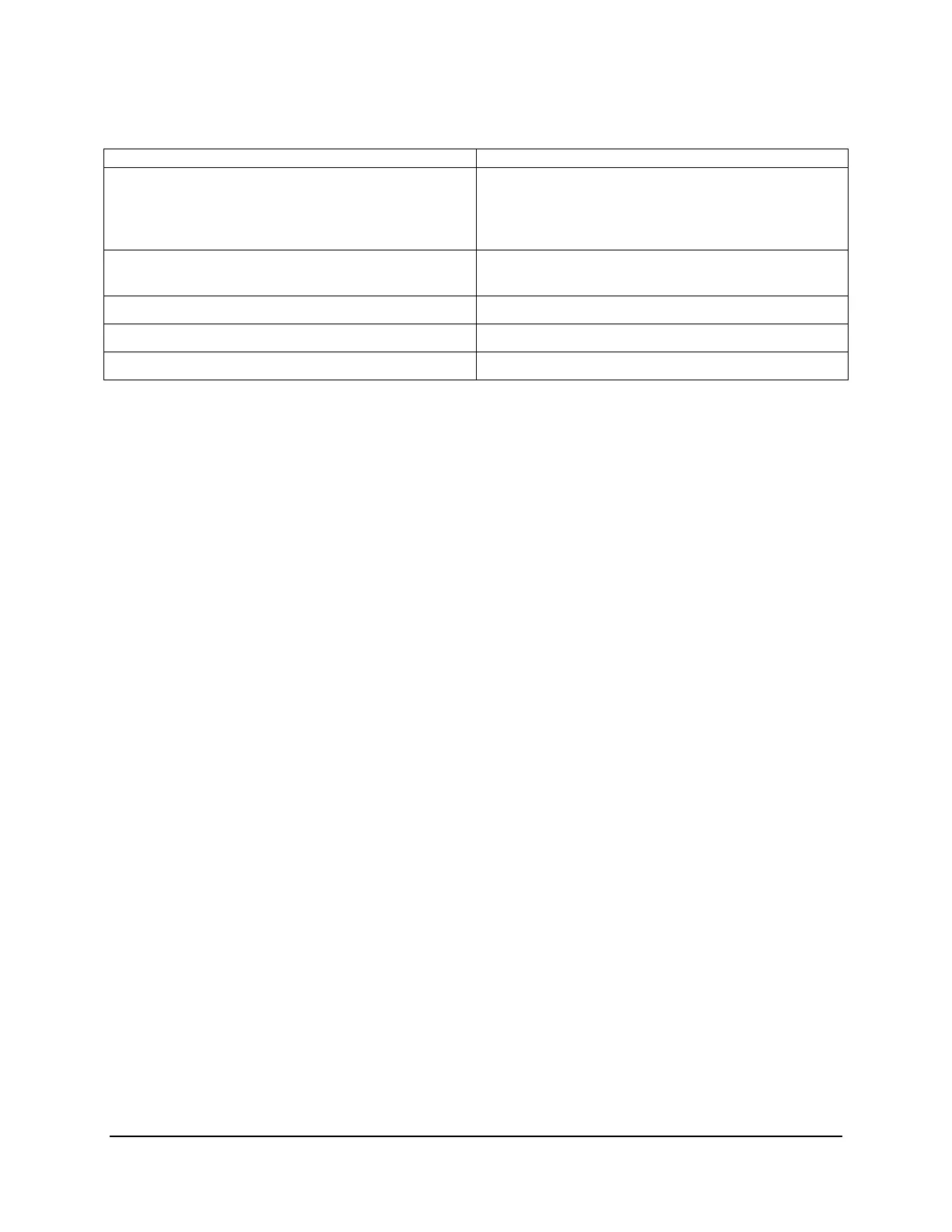

Table 5. Intel

®

Xeon

®

Processor 5500 Series Feature Set Overview

Intel® Xeon® Processor 5500 Series and 5600 Series

Instruction Cache = 32 KB

Data Cache = 32 KB

8 MB shared among cores (up to 4)

Two full-width Intel

®

QuickPath Interconnect links,

up to 6.4 GT/s in each direction.

Up to four cores per processor.

Up to two processors per platform.

The Intel

®

Server Board S5500BC supports Intel

®

Xeon

®

processor 5500 series and 5600 series

with 95 Watt Thermal Design Power (TDP) or less and with a maximum data transfer rate of 6.4

GT/s.

3.1.1 Intel

®

QuickPath Interconnect (QPI)

Intel

®

QuickPath Interconnect (QPI) is a cache-coherent, link-based interconnect specification

developed by Intel to connect processor, chipset and I/O bridge components. The Intel

®

IOH

5500 chipset is the first dual-processor server/workstation platform to implement Intel

®

QuickPath Interconnect links. Figure 13 provides a platform overview of the Intel

®

IOH 5500

chipset with Intel

®

QuickPath Interconnect implementation.

The Intel

®

IOH 5500 chipset supports up to two processor sockets, with up to four cores per

socket. With Intel

®

QuickPath Interconnect, caching agents are responsible for participating in

the cache coherence protocol, and home agents are responsible for managing access to the

memory regions they control. Since the Intel

®

Xeon

®

processor 5500 series contains an

integrated memory controller, the home agents and caching agents reside within the processor

sockets. The Intel

®

QuickPath Interconnect link blocks include the Intel

®

QuickPath Interconnect

Physical through Protocol layers, which are implemented in hardware. No special software or

drivers are required, other than firmware to initialize the Intel

®

QuickPath Interconnect links and

load routing information.

Each the Intel

®

Xeon

®

processor 5500 series and 5600 series is connected to the other

processor and the Intel

®

I/O Hub (IOH) chipset through dedicated Intel

®

QuickPath Interconnect

links. Each Intel

®

QuickPath Interconnect link is a serial point-to-point connection with 20 lanes

per link under full width operation. These links are the only mode of data exchange between the

processors and Intel

®

IOH chipset. There are no sideband signals. The Intel

®

QuickPath

Interconnect communication fabric is glueless and does not require special hardware to

interface to the processors to maintain cache coherency.

Loading...

Loading...