MOTOROLA M68020 USER’S MANUAL 7- 15

The final portion of the cpScc instruction format contains zero to five effective address

extension words. These words contain any additional information required to calculate the

effective address specified by bits 5–0 of the F-line operation word.

7.2.2.2.2 Protocol. Figure 7-8 shows the protocol for the cpScc instruction. The

MC68020/EC020 transfers the condition selector to the coprocessor by writing the word

following the F-line operation word to the condition CIR. The main processor then reads

the response CIR to determine its next action. The coprocessor can return a response

primitive to request services necessary to evaluate the condition. The operation of the

cpScc instruction depends on the condition evaluation indicator returned to the main

processor by the coprocessor. When the coprocessor returns the false condition indicator,

the main processor evaluates the effective address specified by bits 5–0 of the F-line

operation word and sets the byte at that effective address to FALSE (all bits cleared).

When the coprocessor returns the true condition indicator, the main processor sets the

byte at the effective address to TRUE (all bits set to one).

7.2.2.3 TEST COPROCESSOR CONDITION, DECREMENT, AND BRANCH

INSTRUCTION. The operation of the test coprocessor condition, decrement, and branch

instruction is similar to that of the DBcc instruction provided in the M68000 family

instruction set. This operation uses a coprocessor-evaluated condition and a loop counter

in the main processor. It is useful for implementing DO UNTIL constructs used in many

high-level languages.

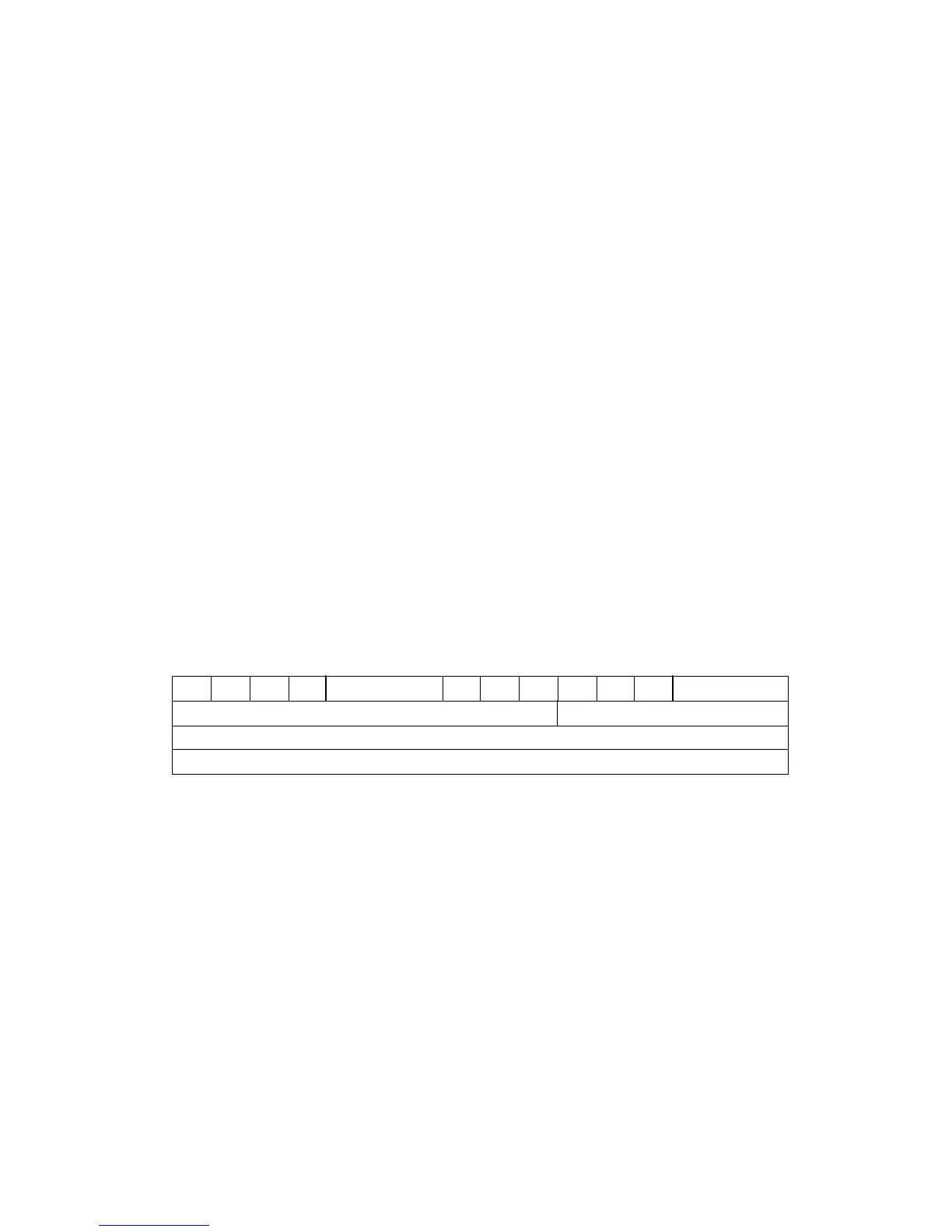

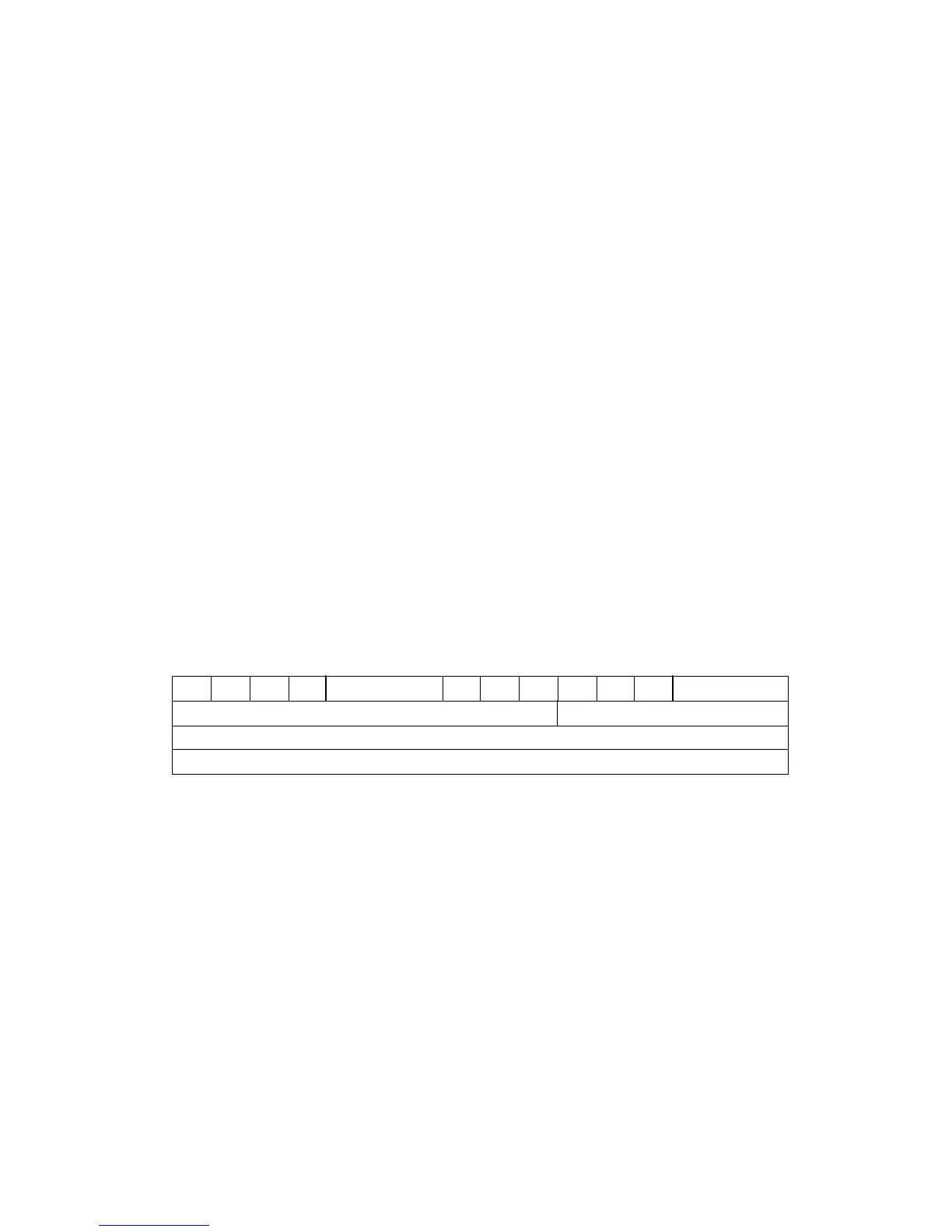

7.2.2.3.1 Format. Figure 7-12 shows the format of the test coprocessor condition,

decrement, and branch instruction, denoted by the cpDBcc mnemonic.

15

CpID

0

EGISTE

PTIONAL COPROCESSOR-DEFINED EXTENSION WORD

ISPLACEMEN

ONDITION SELECTOR

RESERVED

Figure 7-12. Test Coprocessor Condition, Decrement, and Branch

Instruction Format (cpDBcc)

The first word of the cpDBcc instruction, F-line operation word, contains the CpID field in

bits 11–9 and 001001 in bits 8–3 to identify the cpDBcc instruction. Bits 2–0 of this

operation word specify the main processor data register used as the loop counter during

the execution of the instruction.

The second word of the cpDBcc instruction format contains the coprocessor condition

selector field in bits 5–0 and should contain zeros in bits 15–6 (reserved by Motorola) to

maintain compatibility with future M68000 products. This word is written to the condition

CIR to initiate execution of the cpDBcc instruction.

Loading...

Loading...